Parameterising 2/4xcounter module

2 x 32 bit counter with G/RES (mode 27)

12

Parameter setting

12.4

12.4.14

l

12.4-39

EDSPM-TXXX-3.0-04/2004

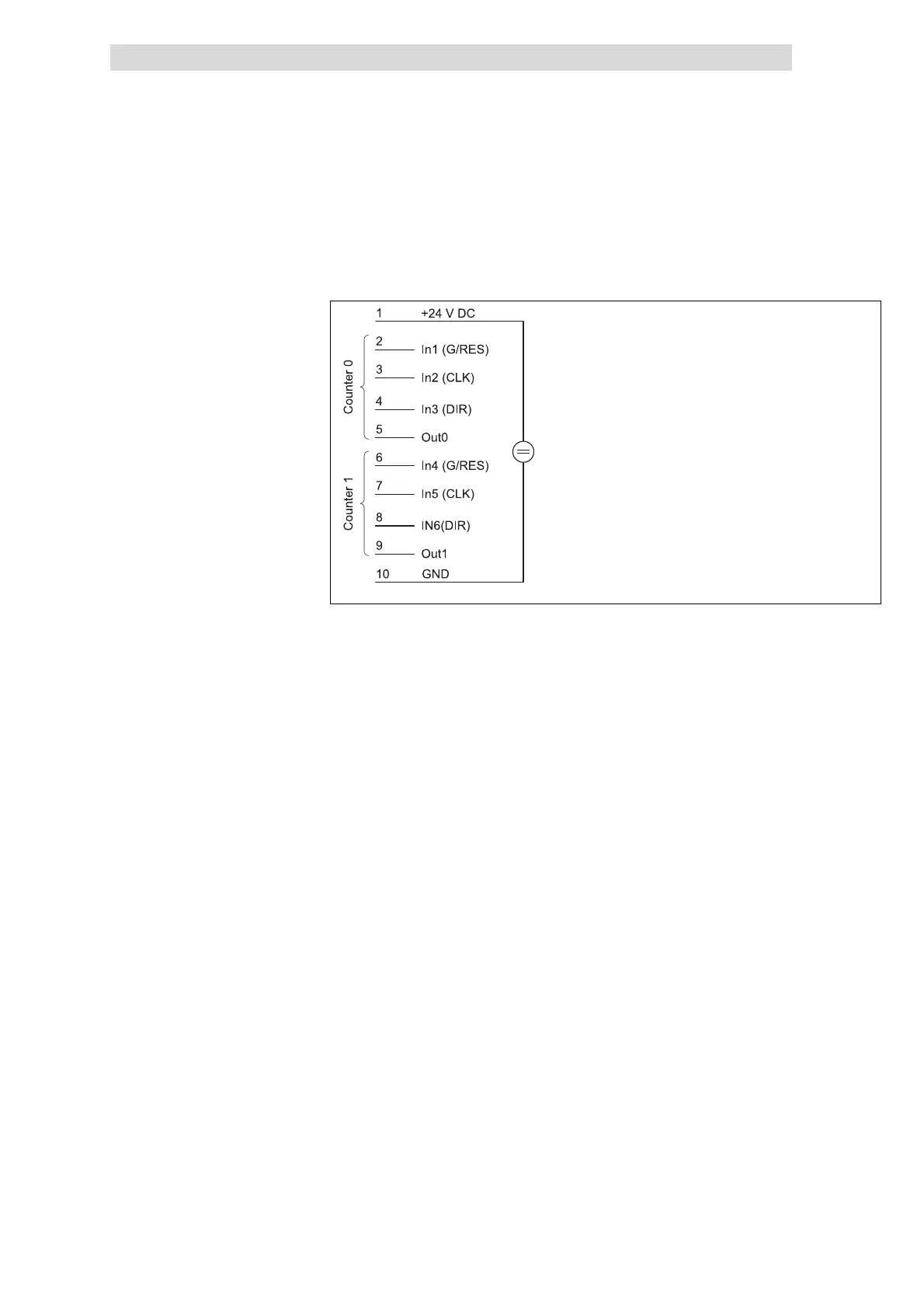

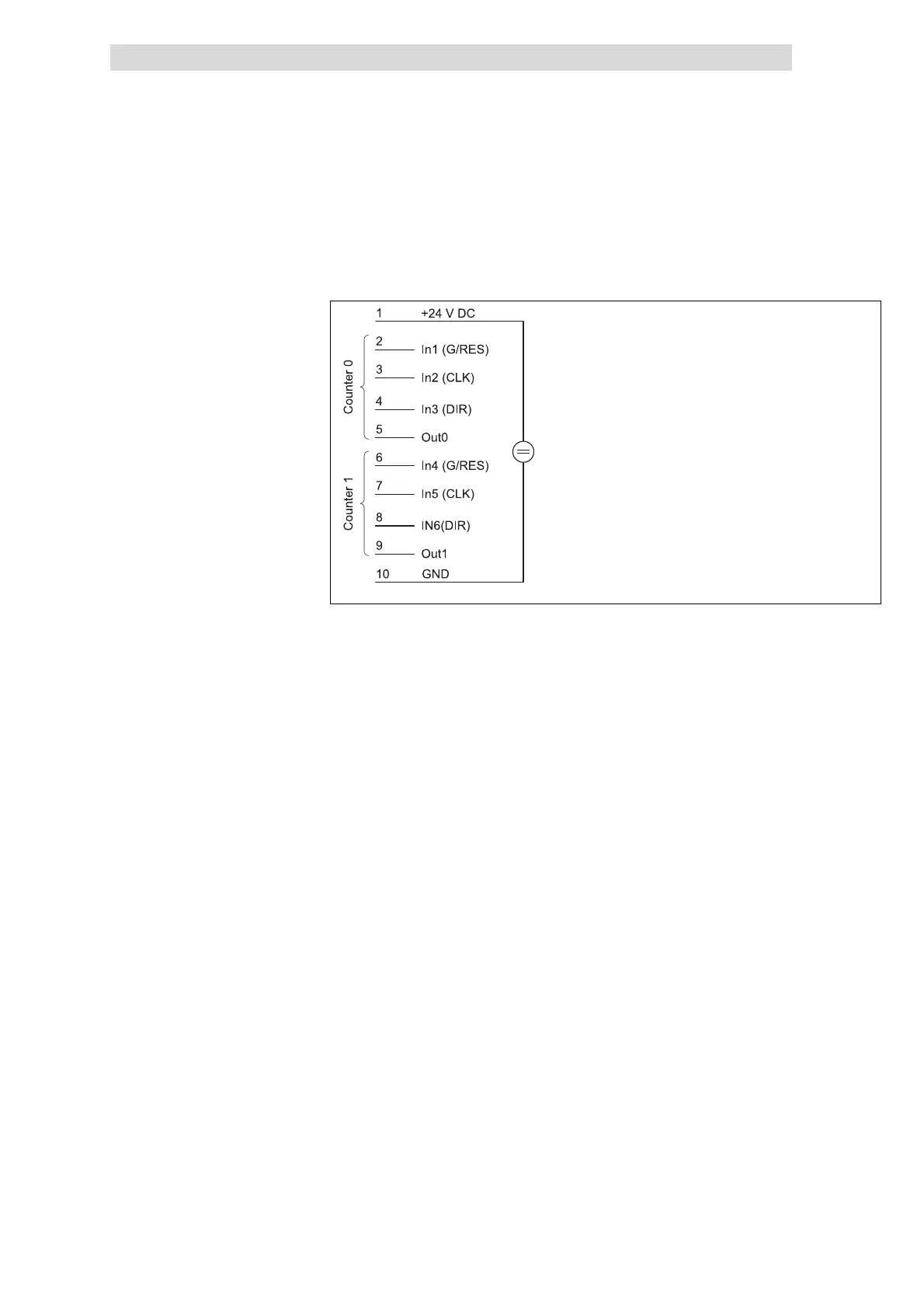

12.4.14 2 x 32 bit counter with G/RES (mode 27)

epm-t142

Fig. 12.4-51 Terminal assignment of the 2/4xcounter in the mode 27

Themode27offerstwo32-bitcounterswhichcanbeassignedwithastarting

value.

The counting direction is determined via the signal level at input IN3 / IN6 (DIR):

Upcounter: LOW level

Downcounter: HIGH level

If a HIGH level is applied to input IN3 / IN6 (G/RES), the counter is incremented or

decremented by 1 with each LOW/HIGH edge.

During the counting process a HIGH level must be applied to input IN1 / IN4

(G/RES). With a LOW level the counter content is frozen. With a rising edge at the

input IN1 / IN4 (G/RES) the counter is deleted.

When the counter reaches zero, the output OUT0 / OUT1 is set to HIGH level for

at least 100 ms, even if the counter continues to count. When the counter stops

at zero, the output OUT0 / OUT1 remains on the HIGH level.

Terminal assignment

DIR signal

CLK signal

G/RES signal

OUT signal

Loading...

Loading...