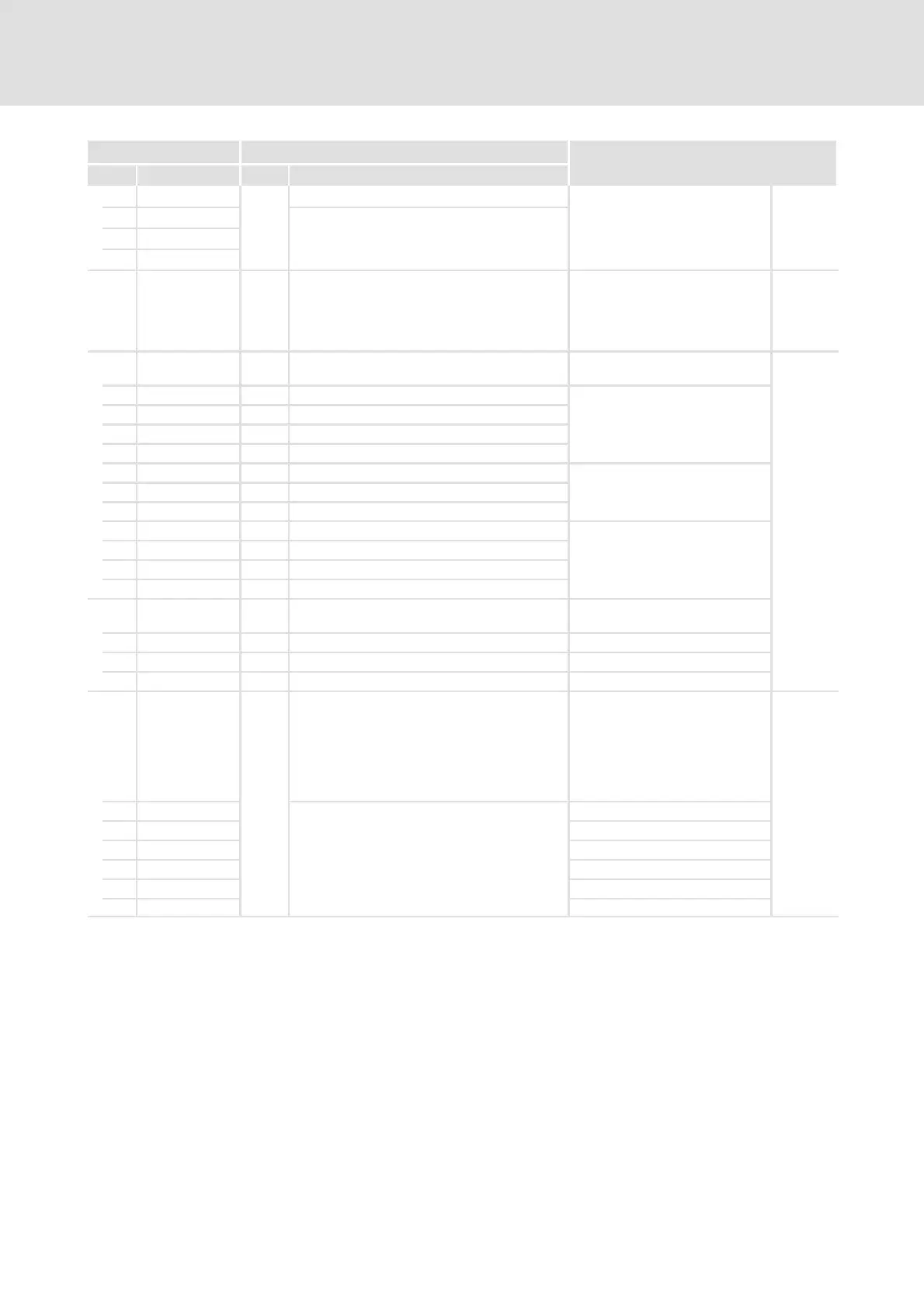

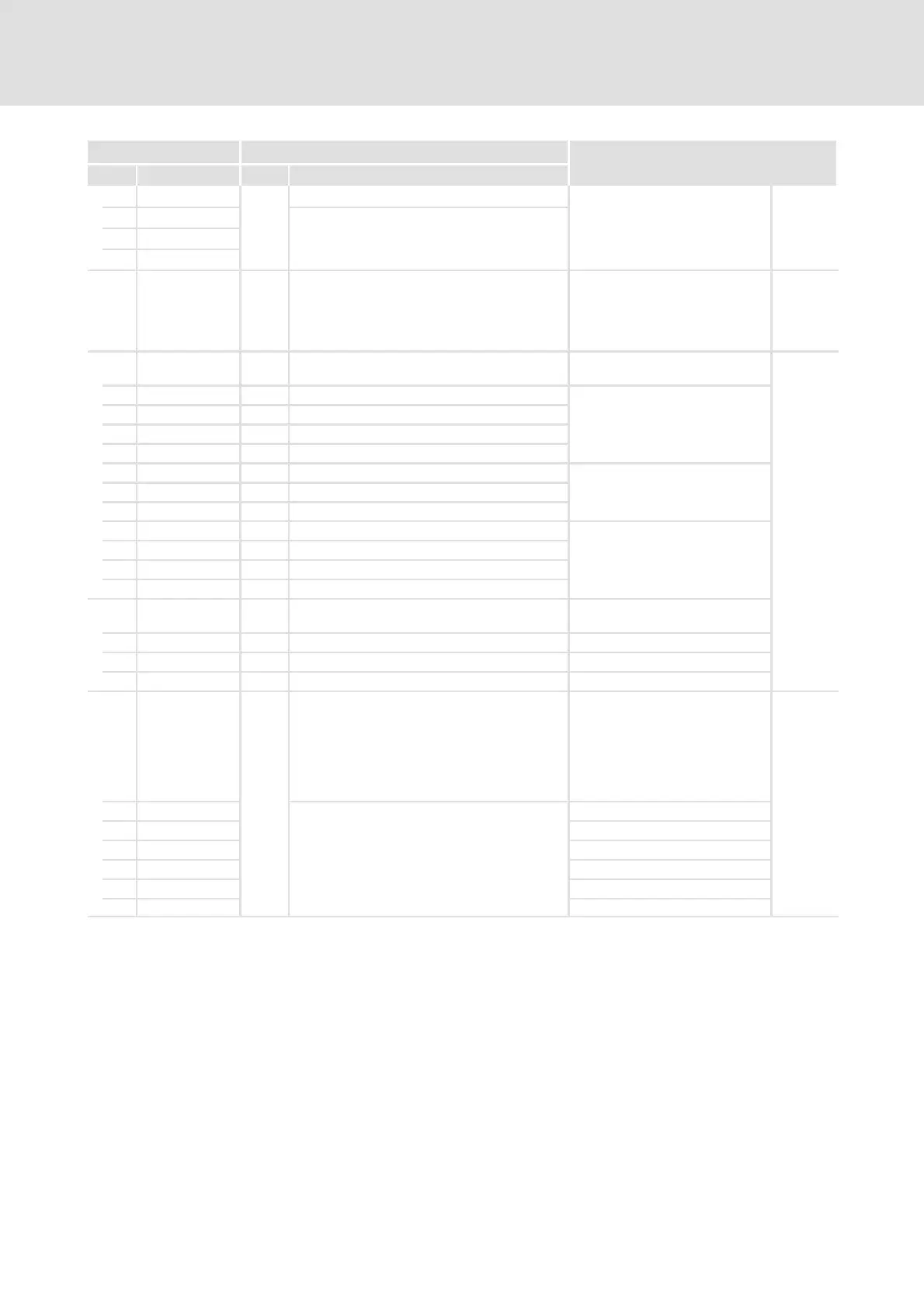

Configuration

Code table

8

8.3

8.3-55

EDSVF9333V EN 3.0-06/2005

IMPORTANTPossible settingsCode

SelectionLenzeNameNo.

C0858 -199.99 {0.01 %} 199.99

Process output words, function

block AIF-OUT

z Display of the signals linked in

C0850

z 100% = 16384

See System

Manual

(extension)

1 DIS: OUT.W1

2 DIS: OUT.W2

3 DIS: OUT.W3

C0859 DIS: OUT.D1 -2147483648 {1} 2147483647 32-bit phase signal, function

block AIF-OUT

z Display of the signal linked in

C0851

z 1 rev. = 65536

See System

Manual

(extension)

C0860

Selection list 1 Configuration of analog input

signals, function block CAN-OUT

See System

Manual

(extension)

1 CFG: OUT1.W1 1000 FIXED0%

CAN-OUT1

2 CFG: OUT1.W2 1000 FIXED0%

3 CFG: OUT1.W3 1000 FIXED0%

4 CFG: OUT2.W1 1000 FIXED0%

5 CFG: OUT2.W2 1000 FIXED0%

CAN-OUT2

6 CFG: OUT2.W3 1000 FIXED0%

7 CFG: OUT2.W4 1000 FIXED0%

8 CFG: OUT3.W1 1000 FIXED0%

CAN-OUT3

9 CFG: OUT3.W2 1000 FIXED0%

10 CFG: OUT3.W3 1000 FIXED0%

11 CFG: OUT3.W4 1000 FIXED0%

C0861

Selection list 3 Configuration of input signals,

function block CAN-OUT

1 CFG: OUT1.D1 1000 FIXED0INC CAN-OUT1

2 CFG: OUT2.D1 1000 FIXED0INC CAN-OUT2

3 CFG: OUT3.D1 1000 FIXED0INC CAN-OUT3

C0863 0 FFFF Process input words, function

block CAN-IN

z Read only

z Bit0...bit15(viabyte5and

byte 6)

z Bit 16 ... bit 31 (via byte 7 and

byte 8)

See System

Manual

(extension)

1 DIS: IN1 dig0 CAN-IN1, bit 0 ... bit 15

2 DIS: IN1 dig16 CAN-IN1, bit 16 ... bit 31

3 DIS: IN2 dig0 CAN-IN2, bit 0 ... bit 15

4 DIS: IN2 dig16 CAN-IN2, bit 16 ... bit 31

5 DIS: IN3 dig0 CAN-IN3, bit 0 ... bit 15

6 DIS: IN3 dig16 CAN-IN3, bit 16 ... bit 31

Loading...

Loading...