RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1241

Dec 10, 2015

17.5.3 Buffer Processing of Transmission Data

(1) Transmission of UART Buffer

For a 9-byte transmission, the contents stored in the LUDBn0 and LDBn1 to LDBn8 registers are transmitted to data areas

0 to 8. The LUDBn0 register is used only if 9-byte transmission is set. In other cases, the LDBn1 to LDBn8 registers are

selected depending upon the length of data involved. For a 4-byte transmission, the contents stored in the LDBn1 to LDBn4

registers are transmitted to data areas 1 to 4, but the contents of the LDBn5 to LDBn8 registers are not transmitted. A LINn

transmission interrupt is generated after the transmission of the data that is set in the MDL[3:0] bits in the LDFCn register (n

= 0, 1). The spaces between transmission data items can be set in the IBS bit in the LSCn register.

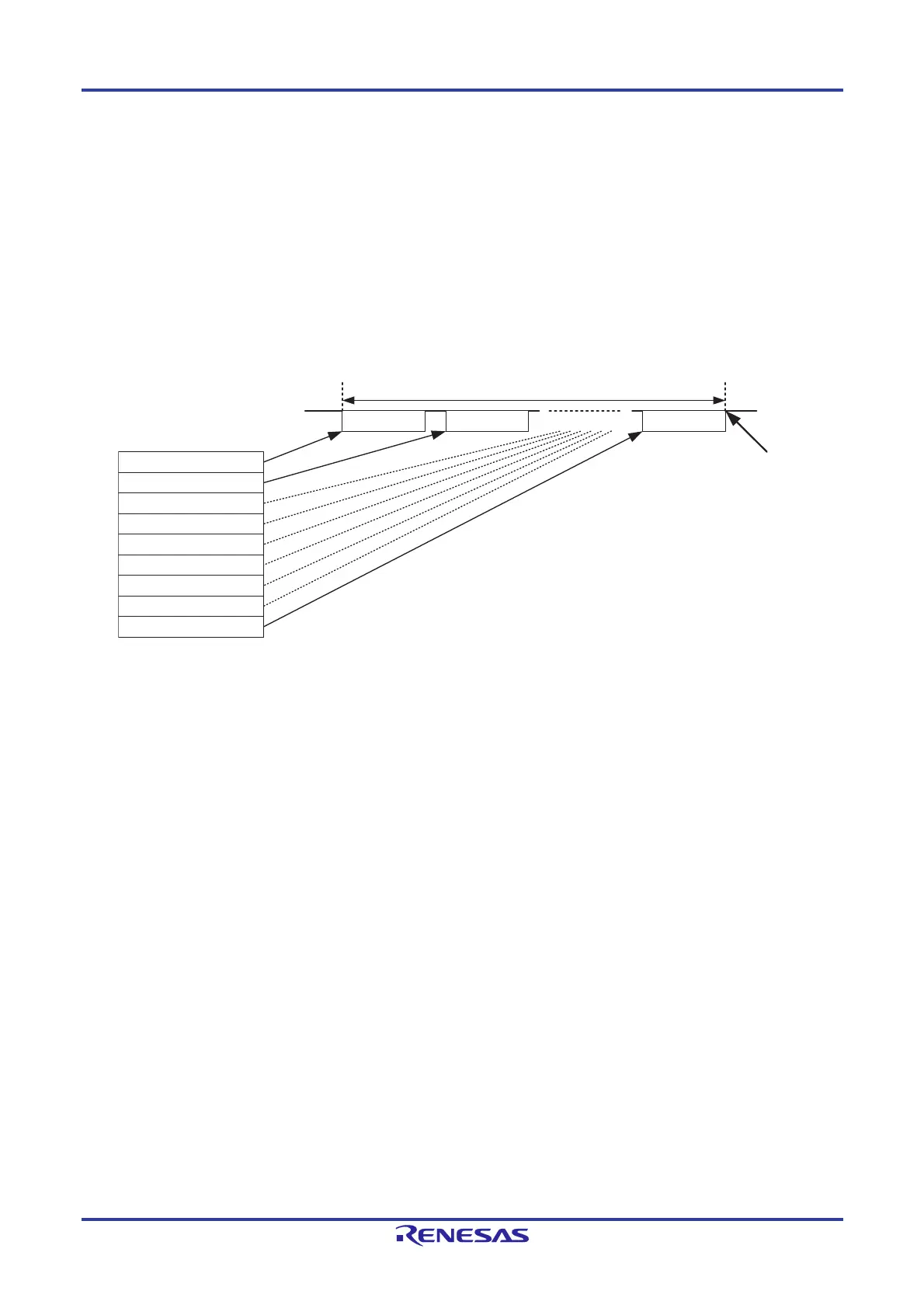

Figure 17-38 shows a 9-byte UART buffer and the transmission processing.

Figure 17-38. UART Buffer and Transmission Processing (for 9-Byte Transmission)

Data 0 Data 1 Data 8

RTS bit in the

LTRCn register

cleared

LUDBn0 register

LDBn1 register

LDBn2 register

LDBn3 register

LDBn4 register

LDBn5 register

LDBn6 register

LDBn7 register

LDBn8 register

Loading...

Loading...