RL78/F13, F14 CHAPTER 24 RESET FUNCTION

R01UH0368EJ0210 Rev.2.10 1553

Dec 10, 2015

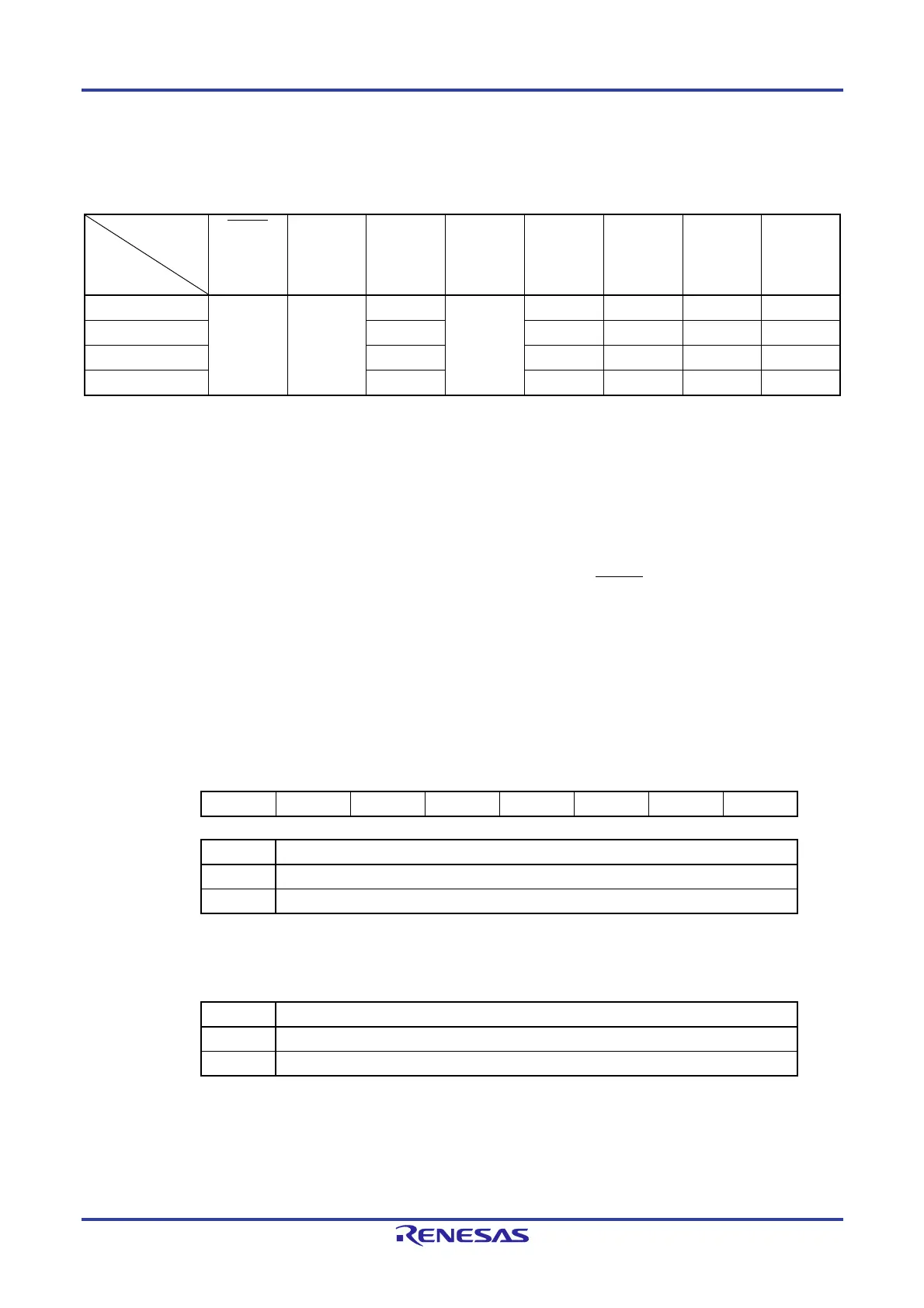

The states of bits in the RESF register when reset requests are generated is shown in Table 24-4.

Table 24-4. States of Bits in the RESF Register When Reset Requests are Generated

Reset Source

Flag

RESET

Input

Reset by

POR

Reset by

Execution of

Illegal

Instruction

Reading

from RESF

Reset by

WDT

Reset by

clock

monitor

Reset by

illegal-

memory

access

Reset by

LVD

TRAP bit Cleared (0) Cleared (0) Set (1) Cleared (0) Held Held Held Held

WDCLRF bit Held Set (1) Set (1) Held Held

IAWRF bit Held Held Held Set (1) Held

LVIRF bit Held Held Held Held Set (1)

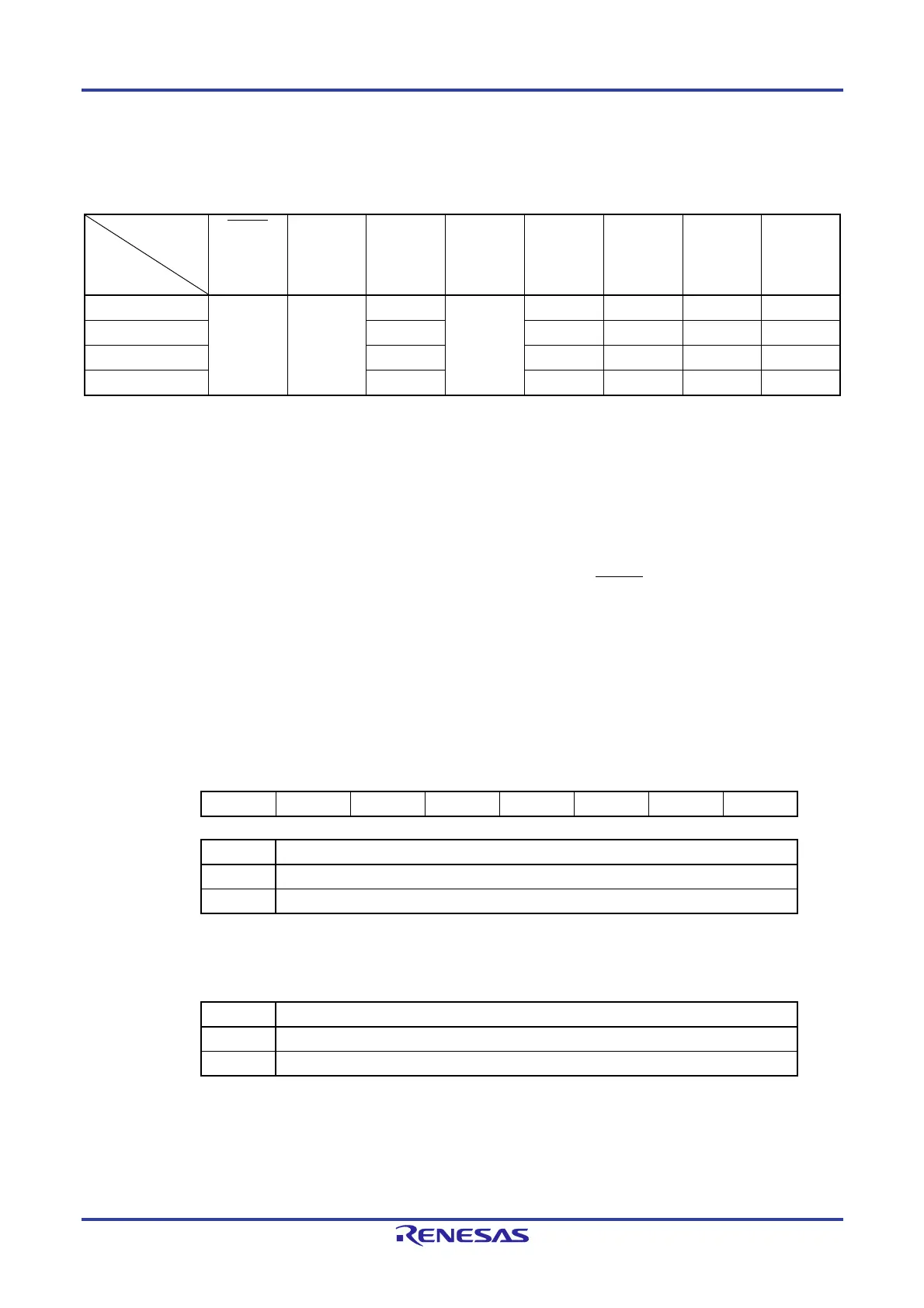

24.1.2 POR/CLM reset confirmation register (POCRES)

The POR/CLM reset confirmation register (POCRES) is used to check whether a reset has been generated by a power-

on reset or a clock-monitor reset.

When writing, the only effective value for the POCRES0 bit is 1. Writing 0 to this bit is ignored.

When writing, the only effective value for the CLKRF bit is 0. Writing 1 to this bit is ignored.

Set the POCRES register by a 1-bit or 8-bit memory manipulation instruction.

The POCRES0 bit only becomes 0 after a reset when the reset was generated by the power-on reset (POR) circuit.

The CLKRF bit becomes 0 after a reset when the reset was generated by the RESET input or power-on reset (POR)

circuit.

Remark For confirming whether a reset was by the power-on reset (POR) circuit, the POCRES0 must be set to 1

beforehand.

Figure 24-6. Format of POR Reset Register (POCRES)

ddress: F02C9H After reset: 00H

Note

R/W

Symbol 7 6 5 <4> 3 2 1 <0>

POCRES 0 0 0 CLKRF 0 0 0 POCRES0

POCRES0 Internal reset request by POR reset

0 A POR request was generated or nothing has been written to this bit.

1 POR request is not generated.

Note The value immediately before a reset is retained when a reset is from any source other than the

POR circuit.

CLKRF Internal reset request by clock monitor

0 Internal reset request is not generated, or the CLKRF bit is cleared.

1 Internal reset request was generated.

Table 24-5 shows the states of bits in the POCRES register when reset requests are generated.

Loading...

Loading...