RL78/F13, F14 CHAPTER 1 OVERVIEW

R01UH0368EJ0210 Rev.2.10 25

Dec 10, 2015

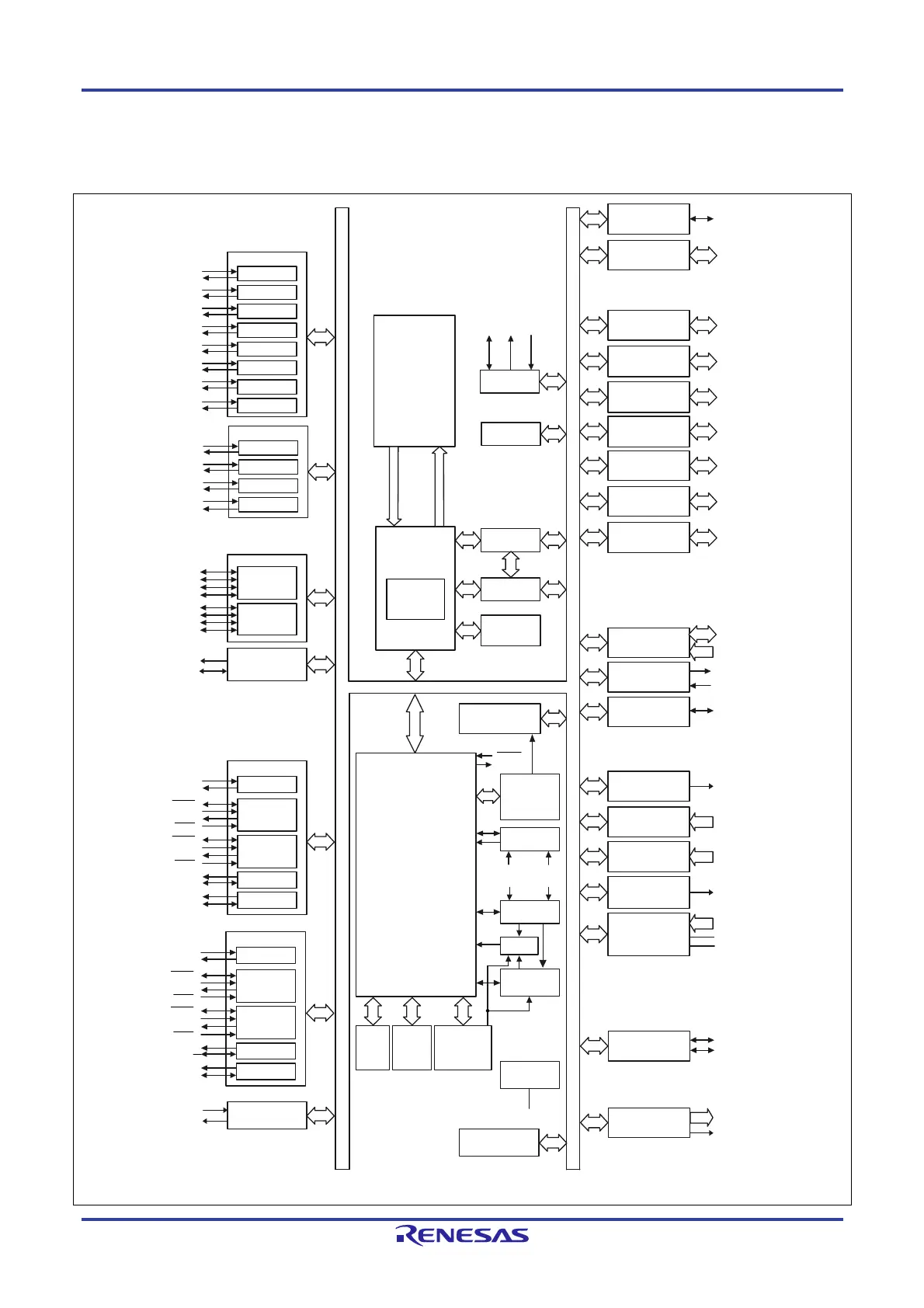

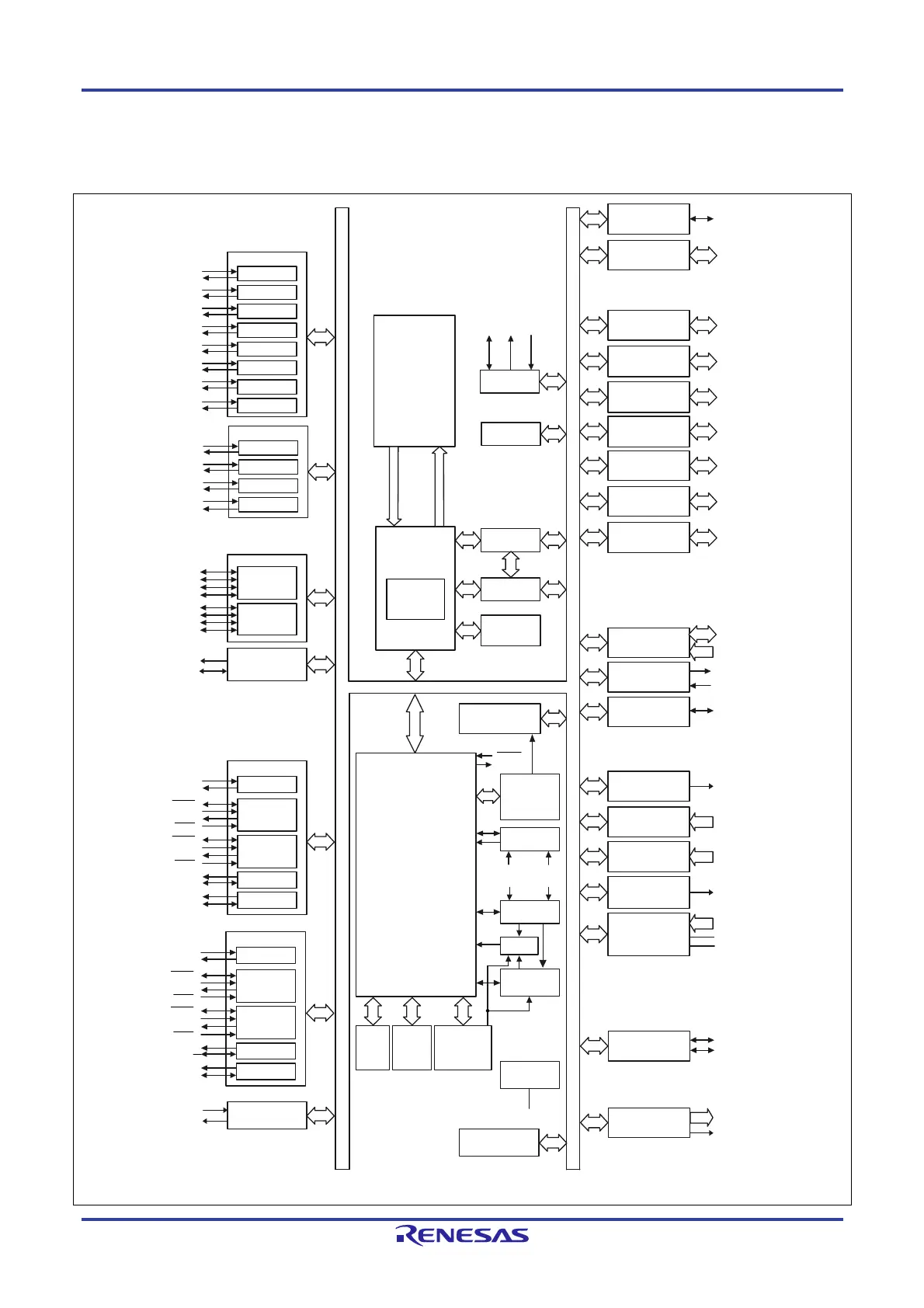

1.4.16 RL78/F13: Block Diagram of R5F10ALn (n = F, G) (LIN incorporated) 64-pin Products

Figure 1-16. Block Diagram

4

8

12

19

TI00

TO00

TI01

TO01

TI02

TO02

TI03

TO03

TI04

TO04

TI05

TO05

TI06

TO06

TI07

TO07

TRDIOB0

TRDIOA0/TRDCLK0

TRDIOC0

TRDIOD0

TRDIOA1

TRDIOB1

TRDIOC1

TRDIOD1

TRJO0

TRJIO0

RXD0

TXD0

SI00

SO00

SI01

SO01

SCL00

SDA00

SCL01

SDA01

LRXD0

LTXD0

LIN0

(1ch)

CSI01

IIC01

IIC00

CSI00

UART0

SAU0 (2ch)

TRJ

ch1

ch0

TRD (2ch)

TAU0 (8ch)

ch00

ch01

ch02

ch03

ch04

ch05

ch06

ch07

PORT0 P00

P10 to P17PORT1 8

P30 to P34PORT3 5

P40 to P43PORT4 4

P50 to P53PORT5 4

P60 to P63PORT6 4

P70 to P77PORT7 8

P80 to P87PORT8 8

P90 to P96PORT9 7

P120, P125

PORT12

P121 to P124

P130

PORT13

P137

P140PORT14

PCLBUZ0PCL/BUZ

KR0 to KR7

KEY RETURN

(8ch)

External INT

(12ch)

RTC

10-bit ADC

(19ch)

INTP0 to INTP11

RTC1HZ

ANI0 to ANI15,

ANI24 to ANI26

AV

REFP

AVREFM

CRC

REGC

Voltage

REGULATOR

PLL

CLM

Main OSC

X1

XT1

X2/EXCLK

XT2/EXCLKS

TOOL

RXD

TOOL

TXDTOOL0

OCD

BCD

INT

DTC

RAM

WWDT

RESET

High-speed

OCO

Low-speed

OCO

POR/

LVD

Clock Generator

+

Reset Generator

CODE FLASH

DATA FLASH

Low-speed

OCO (for WDT)

Sub OSC

Caution Do not use the XT1 and XT2 pin functions in grade-Y products.

RL78

CPU CORE

Multiplier,

Divider and

Multiply-

Accumulator

SCK00

SSI00

SCK01

SSI01

RXD1

TXD1

SI10

SO10

SI11

SO11

SCL10

SDA10

SCL11

SDA11

CSI11

IIC11

IIC10

CSI10

UART1

SAU1 (2ch)

SCK10

SSI10

SCK11

SSI11

2

SCLA0IICA0

(1ch)

SDAA0

RESOUT

RTC1HZ

8

SNZOUT0 to SNZOUT7

STANDBY

TI10

TO10

TI11

TO11

TI12

TO12

TI13

TO13

TAU1 (4ch)

ch10

ch11

ch12

ch13

<R>

Loading...

Loading...