RL78/F13, F14 CHAPTER 27 SAFETY FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1599

Dec 10, 2015

27.3.5 Clock monitor

The clock monitor samples the main system clock (f

MAIN) and main system/PLL select clock (fMP) by using the low-speed

on-chip oscillator. When oscillation of the main system clock stops, a reset request signal (RESCLM) is generated. When

the main system/PLL select clock (f

MP) stops, the clock through mode is forcibly selected and SELPLLS is cleared (but

SELPLL is not).

At the same time, an interrupt request signal (INTCLM) is generated.

(1) Configuration

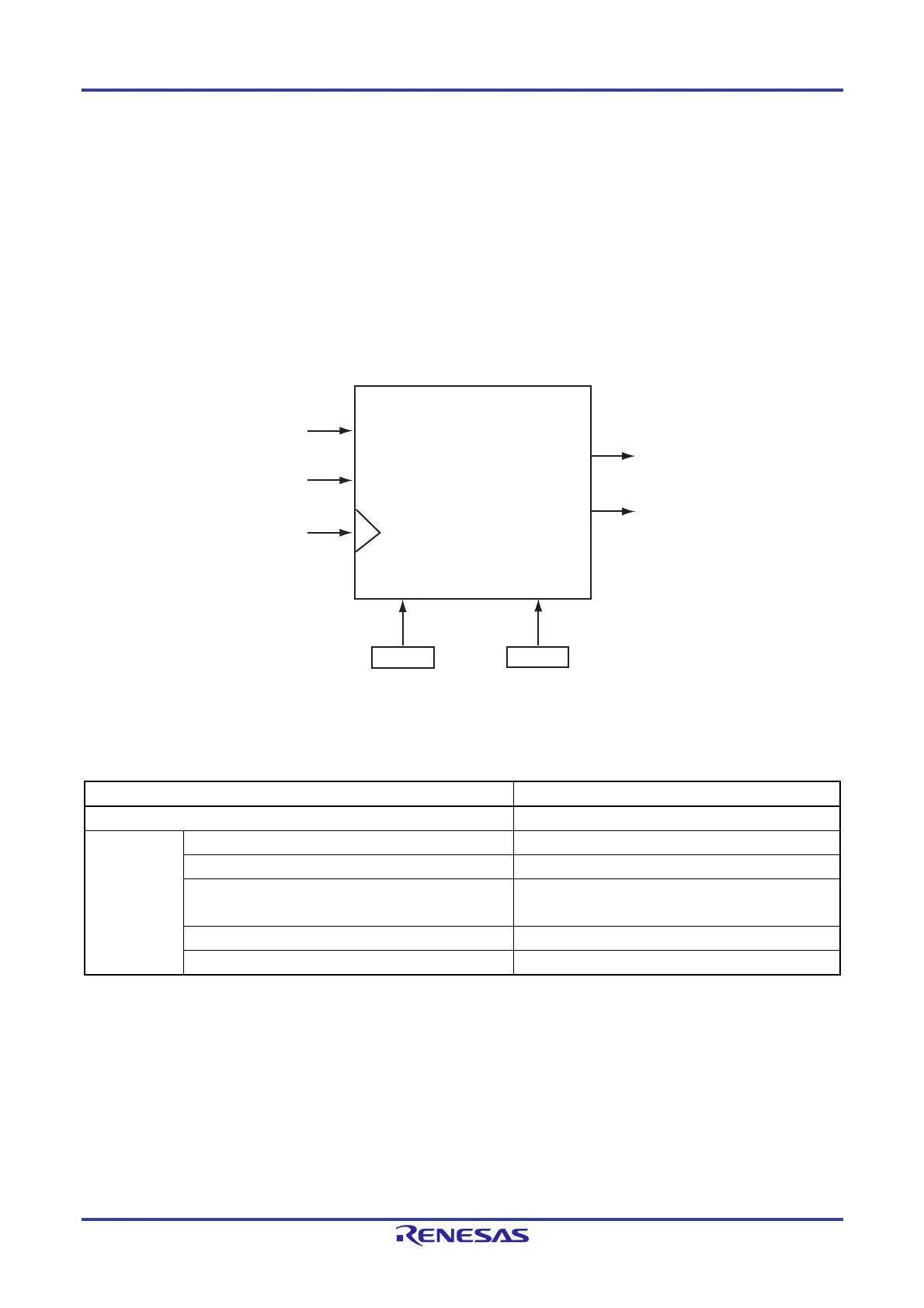

Figure 27-18 shows a block diagram of the clock monitor.

Figure 27-18. Block Diagram of Clock Monitor

Table 27-1. Operating State of Clock Monitor

Operating State of Clock Monitor State of Clock Monitor

fCLK = fSUB or fIL Stopped

fCLK = fMP/2

N

STOP mode Stopped

SNOOZE mode Stopped

Oscillation stabilization time after setting of the MCM0

bit

Stopped

CLKMB = 1 Stopped

CLKMB = 0 Operating

CSS

CPU/peripheral

hardware clock (f

CLK)

selection

System clock

control register

(CKC)

Option byte

(000C1H)

RESCLM (internal reset signal)

INTCLM (internal interrupt signal)

CLKMB

Enabling/

disabling

Main system clock (f

MAIN)

Main system/PLL select clock (f

MP)

Low-speed on-chip oscillator clock (f

IL)

Loading...

Loading...