RL78/F13, F14 CHAPTER 29 OPTION BYTE

R01UH0368EJ0210 Rev.2.10 1621

Dec 10, 2015

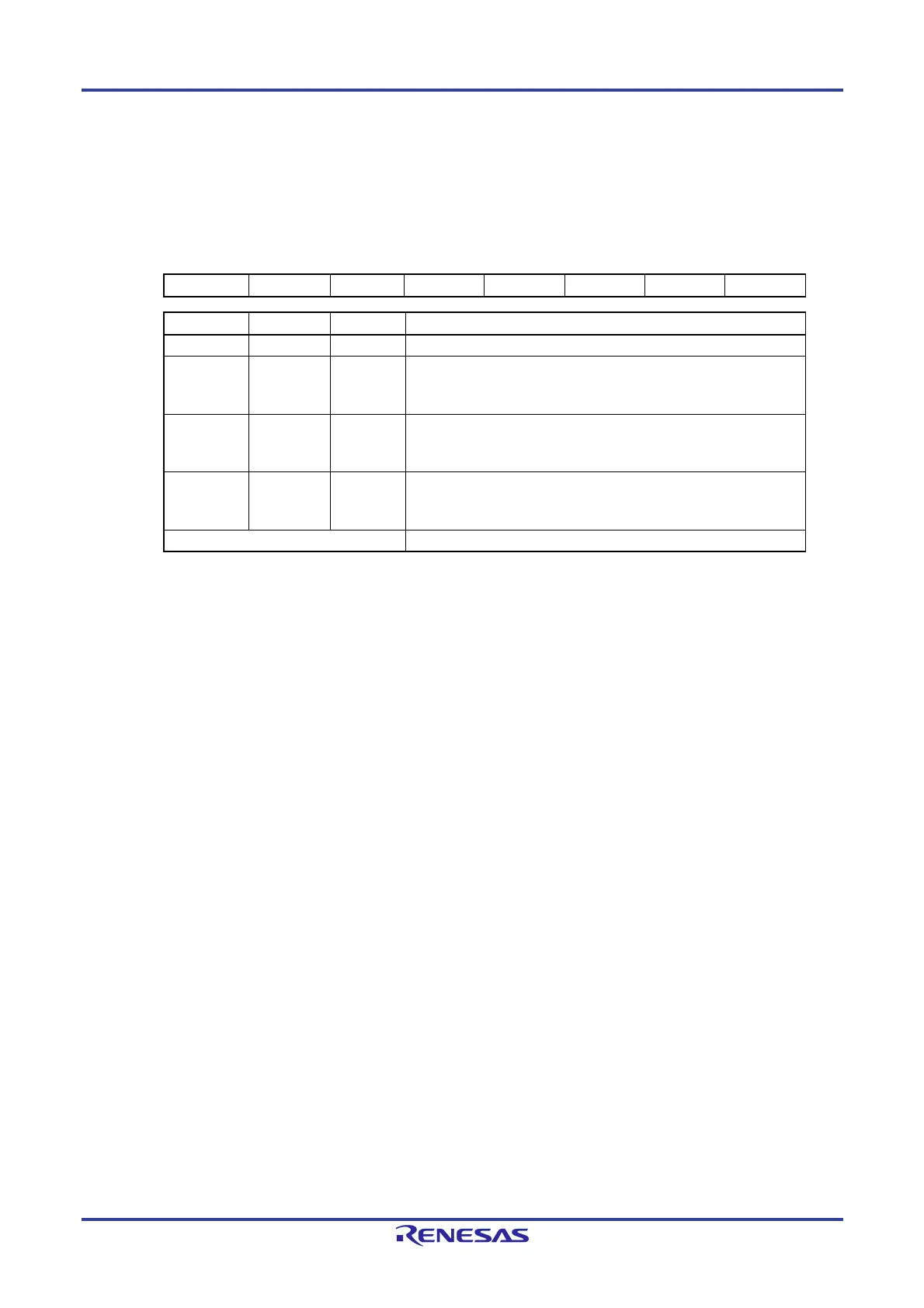

29.3 Format of On-chip Debug Option Byte

The format of on-chip debug option byte is shown below.

Figure 29-4. Format of On-chip Debug Option Byte (000C3H/020C3H)

Address: 000C3H/020C3H

Note 1

7 6 5 4 3 2 1 0

OCDENSET 0 0 0 0 1 HPIEN

Note 2

OCDERSD

OCDENSET HPIEN

Note 2

OCDERSD Control of on-chip debug operation

0 0 0 Disables on-chip debug operation.

1 0 0 Enables on-chip debugging and disables hot plug-in operation.

Erases data of flash memory in case of failures in authenticating on-

chip debug security ID.

1 0 1 Enables on-chip debugging and disables hot plug-in operation.

Does not erase data of flash memory in case of failures in

authenticating on-chip debug security ID.

1 1 1 Enables on-chip debugging and hot plug-in operation.

Does not erase data of flash memory in case of failures in

authenticating on-chip debug security ID.

Other than the above Setting prohibited

Notes 1. Set the same value as 000C3H to 020C3H when the boot swap operation is used because 000C3H is

replaced by 020C3H.

2. When the HPIEN bit is set to 1, the low-speed on-chip oscillator operates and cannot be stopped by the user

program. The low-speed on-chip oscillator can be stopped by register setting only in standby mode. Such

operation is performed because the low-speed on-chip oscillator detects hot plug-in.

Caution Bits 7, 1, and 0 (OCDENSET, HPIEN, and OCDERSD) can only be specified a value.

Be sure to set 00001B to bits 6 to 2.

Remark The value on bits 3 and 2 will be written over when the on-chip debug function is in use and thus it will become

unstable after the setting. However, be sure to set the default values (0, 1) to bits 3 and 2 at setting.

Loading...

Loading...