RL78/F13, F14 CHAPTER 8 TIMER RD

R01UH0368EJ0210 Rev.2.10 636

Dec 10, 2015

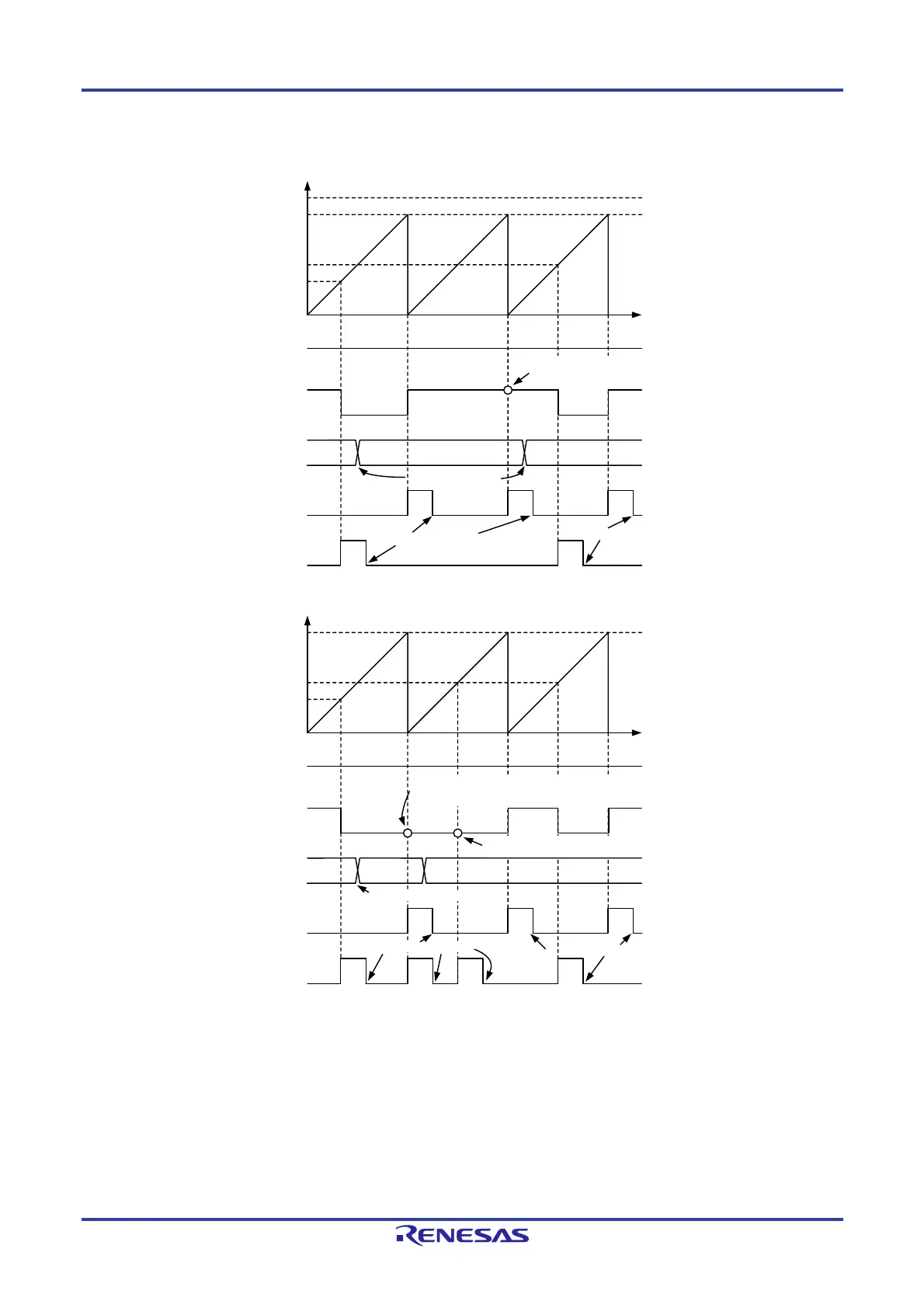

Figure 8-54. Operation Example in PWM Function (Duty Cycle 0%, Duty Cycle 100%)

m

p

q

n

0000H

q

1

p (p>m)n

m

p

n

0000H

1

pn

m

Since no compare match in the TRDGRBi register is

generated, a low level is not applied to the TRDIOBi

output.

Value in TRDi register

TSTARTi bit in

TRDSTR register

TRDIOBi output

TRDGRBi register

IMFB bit in

TRDSRi register

IMFA bit in

TRDSRi register

Value in TRDi register

Set to 0 by a program

Duty cycle 100%

Time

Set to 0 by a program

Time

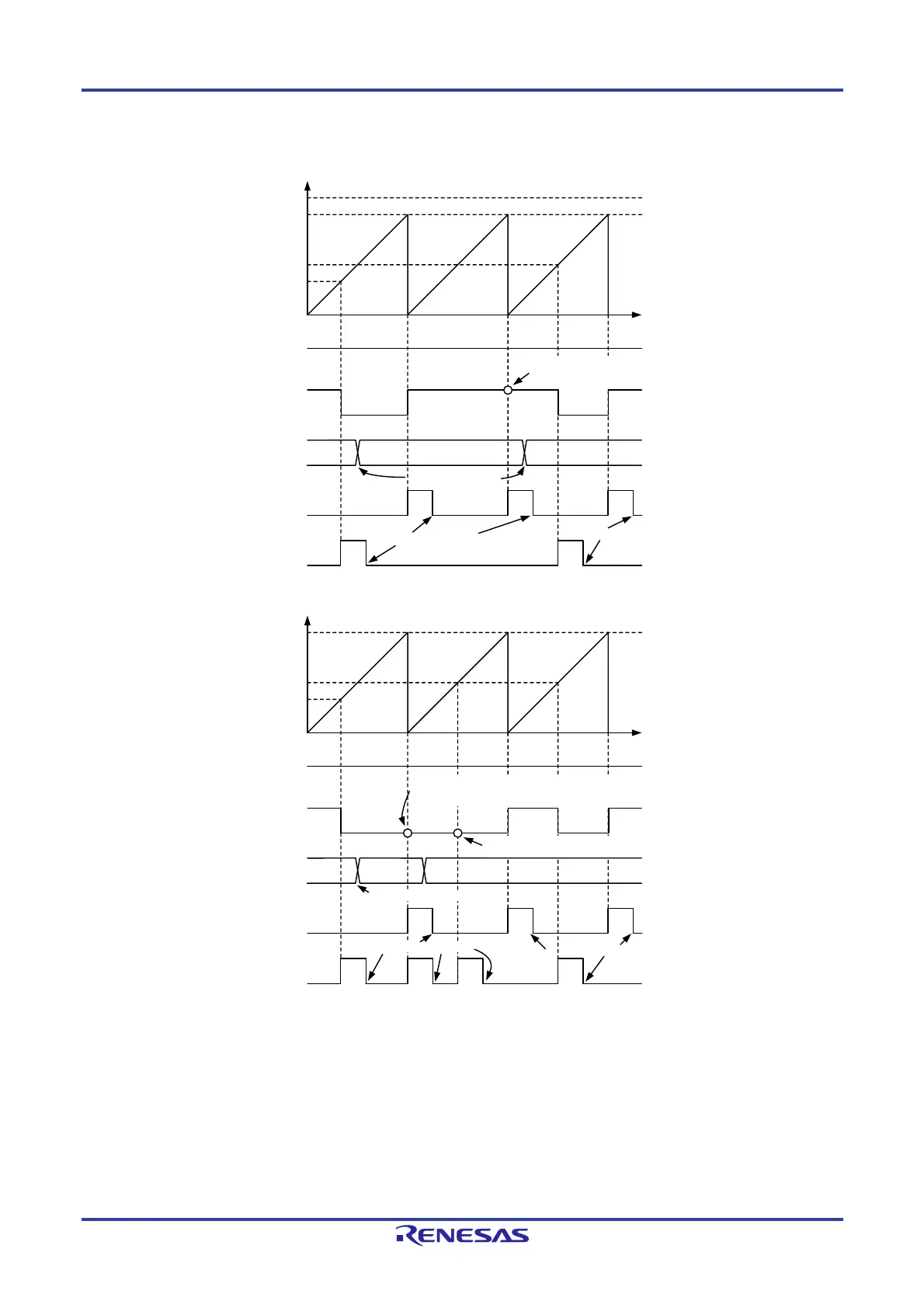

A low level is applied to TRDIOBi output by compare

match with the TRDGRBi register with no change.

Set to 0 by a program

Rewrite by a program

TSTARTi bit in

TRDSTR register

TRDIOBi output

TRDGRBi register

IMFA bit in

TRDSRi register

IMFB bit in

TRDSRi register

Remark

i = 0 or 1

m: Value set in TRDGRAi register

The above diagram applies under the following conditions :

The EBi bit in the TRDOER1 register is set to 0 (TRDIOBi output enabled).

The POLB bit in the TRDPOCRi register is set to 0 (active level is low).

Duty cycle 100%

When compare matches with registers TRDGRAi and TRDGRBi are generated

simultaneously, the compare match with the TRDGRBi register has priority.

A low level is applied to the TRDIOBi output without any change .

Set to 0 by a program

Rewrite by a program

Loading...

Loading...