RL78/F13, F14 CHAPTER 15 SERIAL ARRAY UNIT

R01UH0368EJ0210 Rev.2.10 1005

Dec 10, 2015

15.9.3 Data reception

Data reception is an operation to receive data to the target for transfer (slave) after transmission of an address field. After

all data are received to the slave, a stop condition is generated and the bus is released.

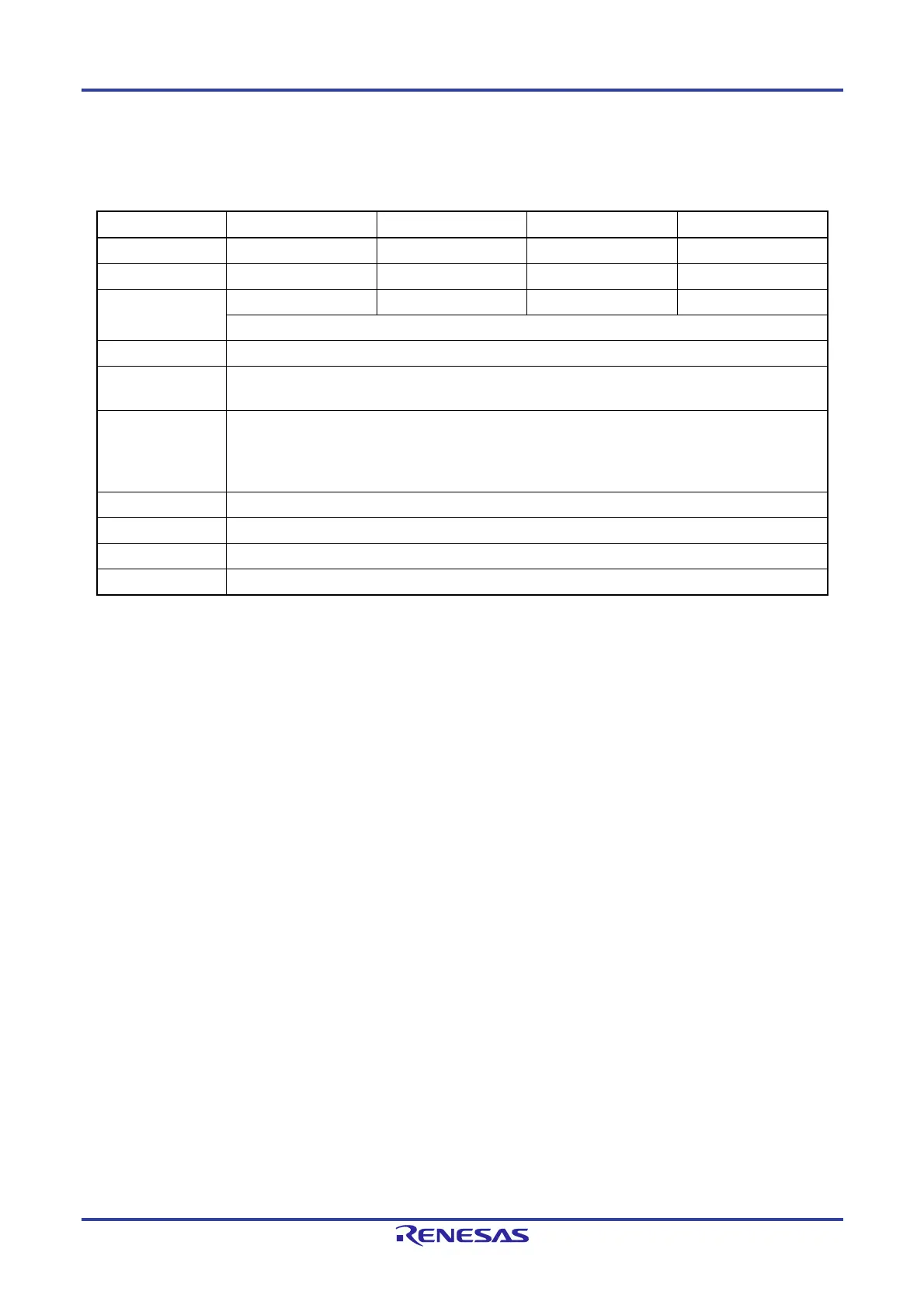

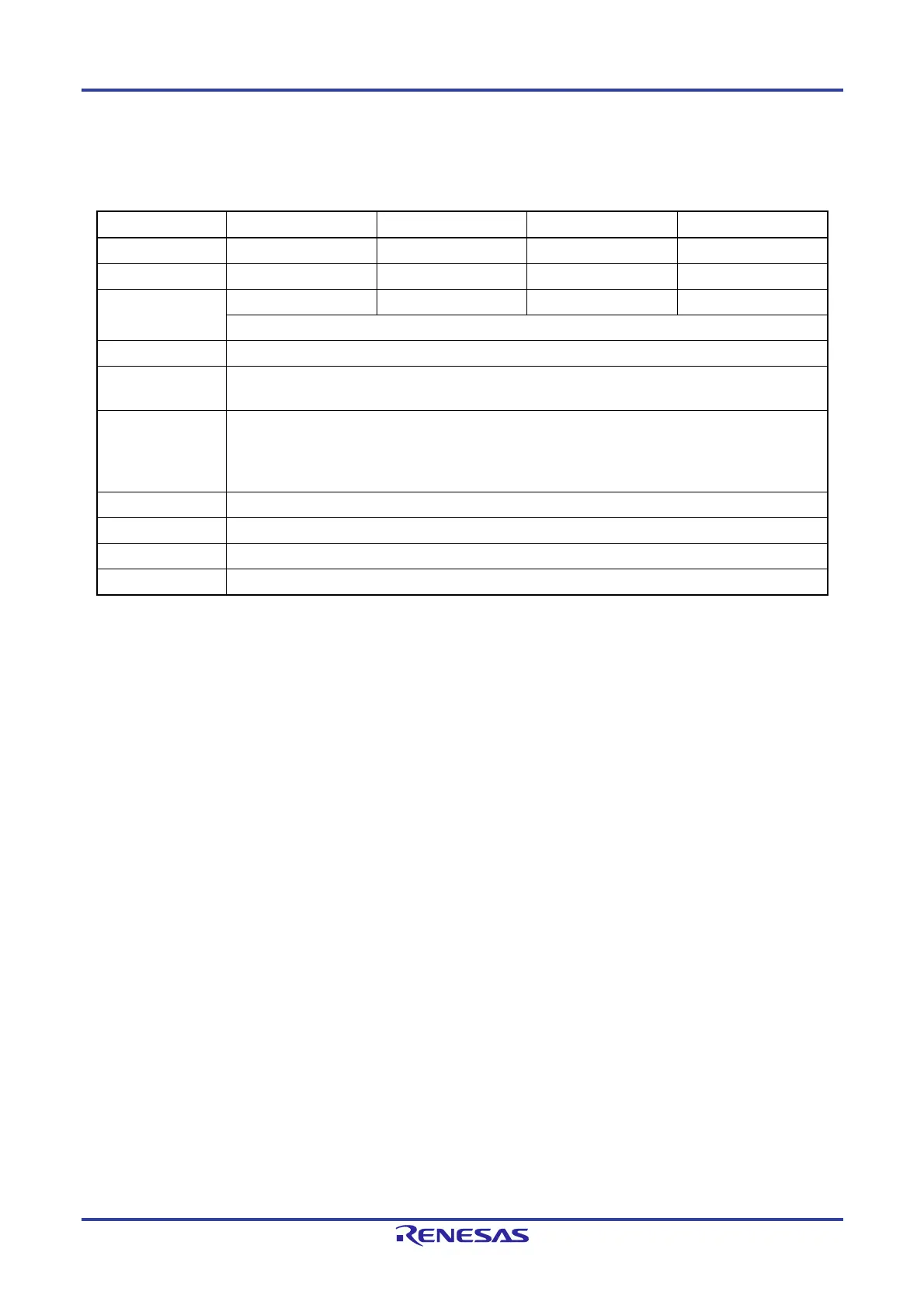

Simplified I

2

C

IIC00 IIC01 IIC10 IIC11

Target channel Channel 0 of SAU0 Channel 1 of SAU0 Channel 0 of SAU1 Channel 1 of SAU1

Pins used SCL00, SDA00

Note

SCL01, SDA01

Note

SCL10, SDA10

Note

SCL11, SDA11

Note

Interrupt INTIIC00 INTIIC01 INTIIC10 INTIIC11

Transfer end interrupt only (Setting the buffer empty interrupt is prohibited.)

Error detection flag Overrun error detection flag (OVFmn) only

Transfer data

length

8 bits

Transfer rate Max. fMCK/4 [Hz] (SDRmn[15:9] = 1 or more) fMCK: Operation clock frequency of target channel

However, the following condition must be satisfied in each mode of I

2

C.

• Max. 400 kHz (first mode)

• Max. 100 kHz (standard mode)

Data level Forward output (default: high level)

Parity bit No parity bit

Stop bit Appending 1 bit (ACK transmission)

Data direction MSB first

Note To perform communication via simplified I

2

C, set the N-ch open-drain output (EVDD0 tolerance) mode (POMxx = 1)

for the port output mode registers (POMxx) (see 4.3 Registers Controlling Port Function for details). When IIC00,

IIC01, IIC10, IIC11 communicating with an external device with a different potential, set the N-ch open-drain output

(EV

DD0 tolerance) mode (POMxx = 1) also for the clock input/output pins (SCL00, SCL01, SCL10, SCL11) (see 4.4.4

Connecting to external device with different potential (3 V) for details).

Remark m: Unit number (m = 0, 1), n: Channel number (n = 0, 1), mn = 00, 01, 10, 11

Loading...

Loading...