RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1382

Dec 10, 2015

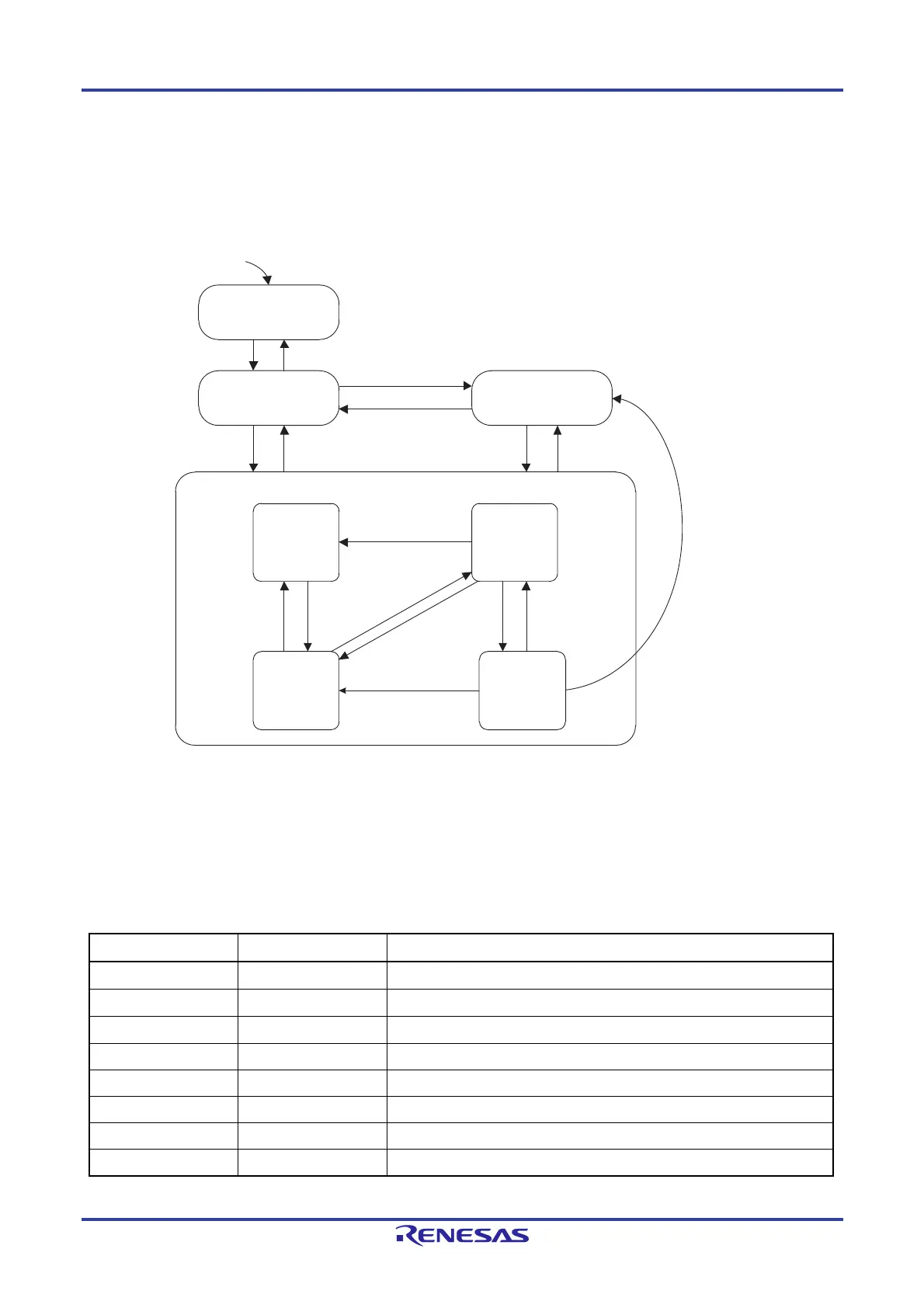

18.4.2 Channel Modes

Figure 18-3 shows a channel mode state transition chart (i = 0). Table 18-7 shows the channel mode transition time (i =

0).

Figure 18-3. Channel Mode State Transition Chart (i = 0)

Table 18-7. Channel Mode Transition Time (i = 0)

Mode before Transition Mode after Transition Maximum Transition Time

Channel stop Channel reset 3 fCLK cycles

Channel reset Channel stop 3 fCLK cycles

Channel reset Channel halt 3 CANi bit times

Channel reset Channel communication 2 CANi bit times

Channel halt Channel reset 3 fCLK cycles

Channel halt Channel communication 3 CANi bit times

Channel communication Channel reset 3 fCLK cycles

Channel communication Channel halt 2 CANi frames

CAN reset

CSLPR = 0

CSLPR = 1

CHMDC[1:0] = B'10

CHMDC[1:0] = B'01

CHMDC[1:0] = B'00

CHMDC[1:0] = B'01

CHMDC[1:0] = B'00

CHMDC[1:0] = B'10

BOSTS = 0

TRMSTS = 0

RECSTS = 1

COMSTS = 1

BOSTS = 0

TRMSTS = 1

RECSTS = 0

COMSTS = 1

SOF

detected

TEC > 255

BOSTS = 0

TRMSTS = 0

RECSTS = 0

COMSTS = 1

BOSTS = 1

TRMSTS = 1

RECSTS = 0

COMSTS =1

Channel stop mode

Channel reset mode

Channel halt mode

Channel communication mode

Arbitration lost

Reception

completed

Tr

an

smissi

on

completed

Tr

ansmission start

11 consecutive

recessive bits have been

detected 128 times

(BOM[1:0] bits are set

to B'00) and transmission

start

11 consecutive recessive bits

have been detected 128 times

(BOM[1:0] bits are set to B'00)

Idle

Reception

Transmission

Bus off

Notes1. Timing of transition from bus off state to channel halt mode

When BOM[1:0] = B'01: Transition to channel halt mode when TEC exceeds 255

When BOM[1:0] = B'10: Transition to channel halt mode when 11 consecutive recessive bits have been detected 128 times

When BOM[1:0] = B'11: Transition to channel halt mode when the CHMDC[1:0] bits are set to B'10

2. While the CAN bus is locked at the dominant level, transition to channel halt mode is not made. In that case, enter channel reset mode.

Remark CHMDC[1:0], CSLPR: Bits in the CiCTRL register (i = 0)

BOM[1:0]: Bits in the CiCTRH register (i = 0)

BOSTS, TRMSTS, RECSTS, COMSTS: Bits in the CiSTSL register (i = 0)

Note 1

Note 2

Loading...

Loading...