RL78/F13, F14 CHAPTER 8 TIMER RD

R01UH0368EJ0210 Rev.2.10 613

Dec 10, 2015

8.3 Operation

8.3.1 Items Common to Multiple Modes

(1) Count Sources

The count source selection method is the same in all modes. However, the external clock cannot be selected

in PWM3 mode.

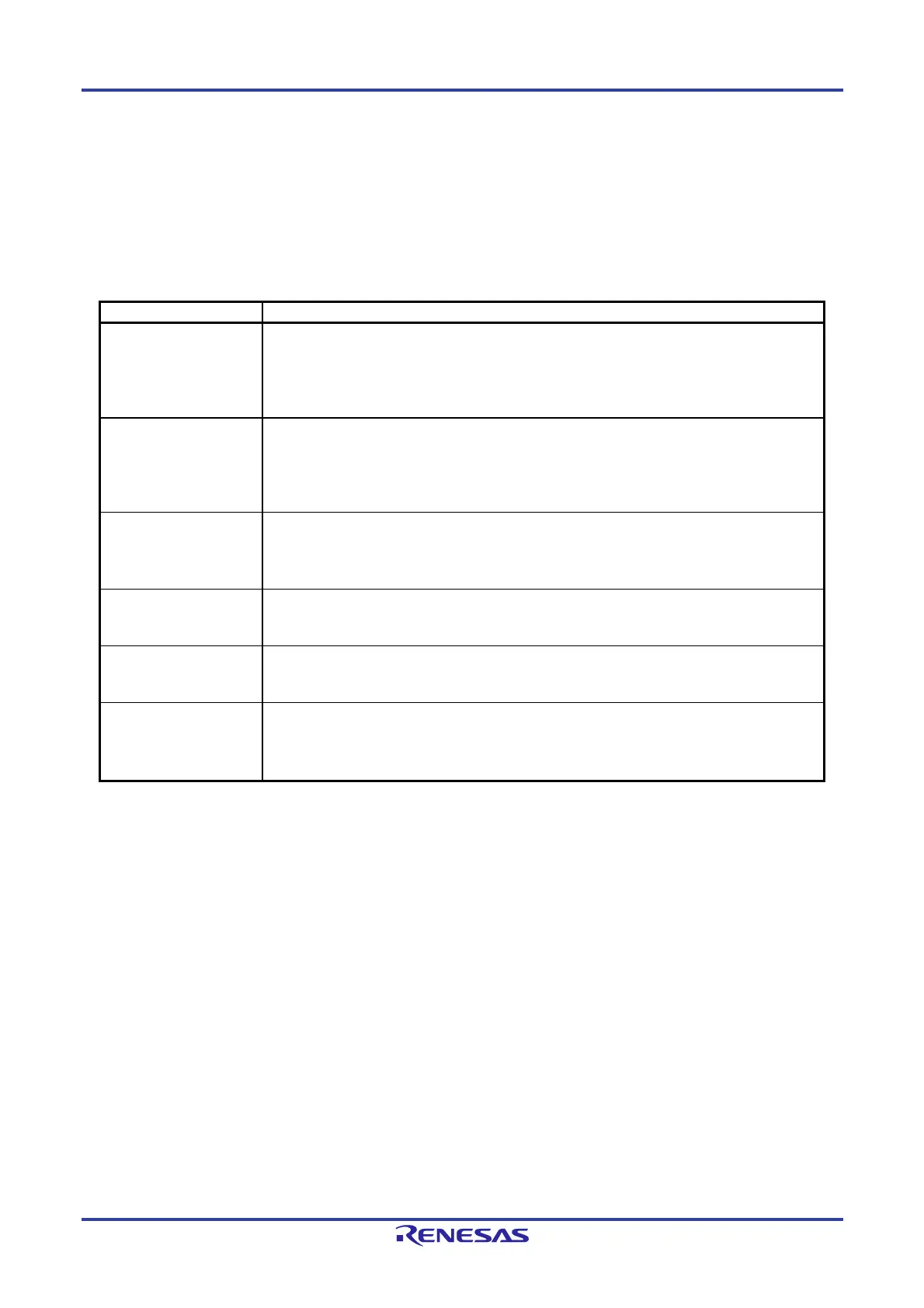

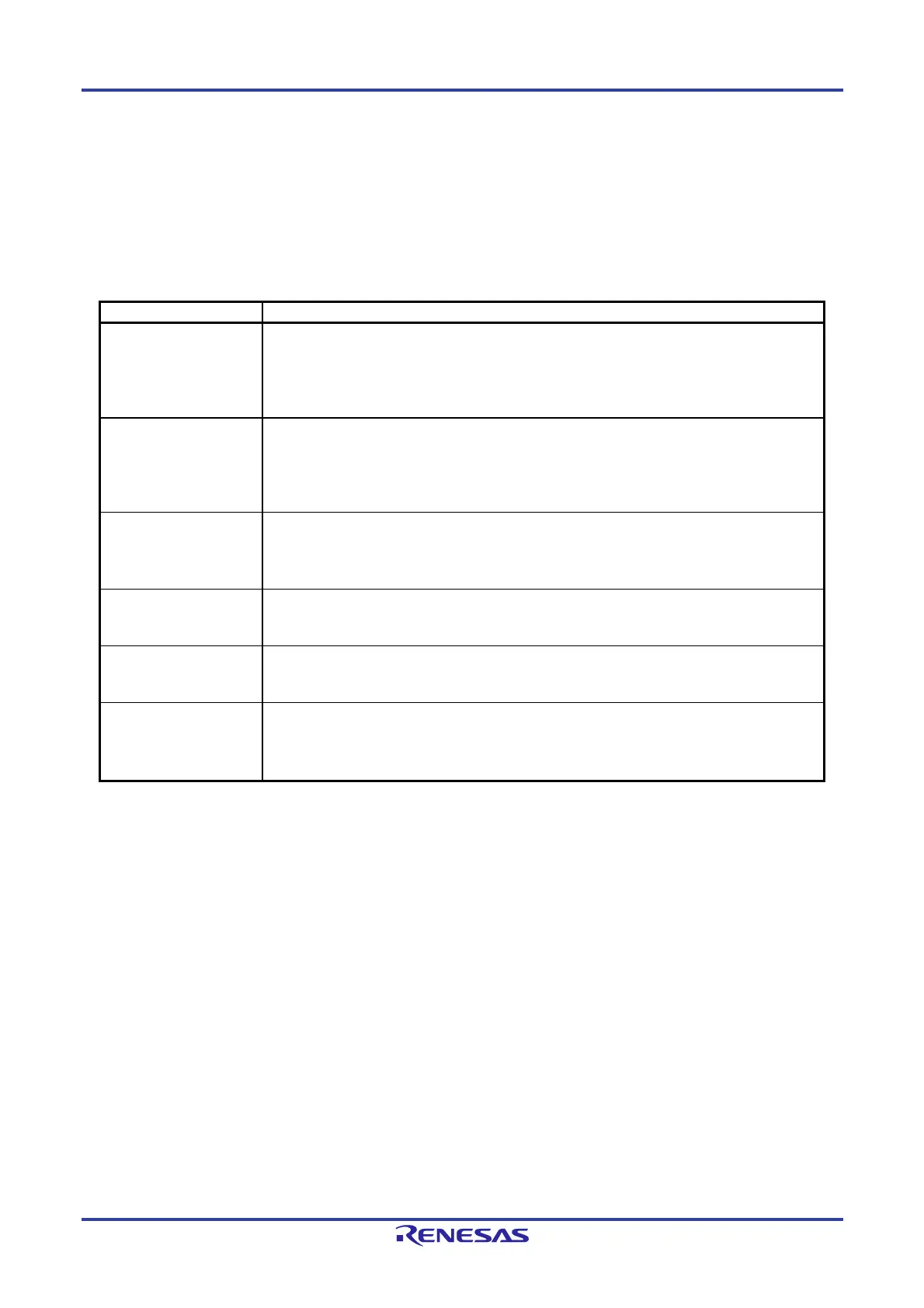

Table 8-11. Count Source Selection

Count Source Selection

fCLK, fCLK/2, fCLK/4, fCLK/8,

f

CLK/32

The FRQSEL4 bit in the user option byte (000C2H/020C2H) is cleared to 0 and the PLLDIV1 bit in

the PLL control register (PLLCTL) is cleared to 0, or the SELPLLS bit in the PLL status register

(PLLSTS) is cleared to 0 and the TRD_CKSEL bit in the clock select register (CKSEL) is cleared to

0.

A count source is selected by bits TCK2 to TCK0 in the TRDCRi register.

fIH The MCM0 bit in the clock system control register (CKC) is cleared to 0, the SELPLL bit in the PLL

control register (PLLCTL) is cleared to 0, the FRQSEL4 bit in the user option byte

(000C2H/020C2H) is set to 1, and the TRD_CKSEL bit in the clock select register (CKSEL) is

cleared to 0.

A count source is selected by bits TCK2 to TCK0 in the TRDCRi register.

fPLL The SELPLL bit in the PLL control register (PLLCTL) is set to 1, the PLLDIV1 bit in the PLL control

register (PLLCTL) is set to 1, the SELPLLS bit in the PLL status register (PLLSTS) is set to 1, and

the TRD_CKSEL bit in the clock select register (CKSEL) is cleared to 0.

The count source is selected by bits TCK2 to TCK0 in the TRDCRi register.

fSUB The SELLOSC bit in the clock select register (CKSEL) is cleared to 0 and the TRD_CKSEL bit in

the clock select register (CKSEL) is set to 1.

A count source is selected by bits TCK2 to TCK0 in the TRDCRi register.

fIL The SELLOSC bit in the clock select register (CKSEL) is set to 1 and the TRD_CKSEL bit in clock

select register (CKSEL) is set to 1.

A count source is selected by bits TCK2 to TCK0 in the TRDCRi register.

External signal input to

TRDCLK0 pin

The STCLK bit in the TRDFCR register is set to 1 (external clock input enabled).

Bits TCK2 to TCK0 in the TRDCRi register are set to 101B.

The active edge is selected by bits CKEG1 and CKEG0 in the TRDCRi register.

The PM bit in the PM register of the port used as a TRDCLK0 pin is set to 1 (input mode).

Remark i = 0 or 1

Loading...

Loading...