RL78/F13, F14 CHAPTER 8 TIMER RD

R01UH0368EJ0210 Rev.2.10 649

Dec 10, 2015

8.5 Notes on Timer RD

8.5.1 SFR Read/Write Access

The timer RD SFRs are undefined when FRQSEL4 = 1 in the user option byte (000C2H/020C2H) and TRD0EN = 0 in

the PER1 register. If it is necessary to read the initial value, set f

CLK to fIH and TRD0EN = 1 before reading.

When setting timer RD, set the TRD0EN bit in the PER1 register to 1 first. If the TRD0EN bit is 0, writes to the timer RD

control registers are ignored and all the read values are the initial values (except for the port registers and the port mode

registers).

The following registers must not be rewritten during count operation:

TRDELC, TRDMR, TRDPMR, TRDFCR, TRDOER1, TRDPTO bit in TRDOER2, TRDDFi, TRDCRi, TRDIORAi,

TRDIORCi, TRDPOCRi

(1) TRDSTR Register

Set the TRDSTR register by an 8-bit memory manipulation instruction.

When the CSELi bit (i = 0 or 1) in the TRDSTR register is set to 0 (count stops at compare match between

registers TRDi and TRDGRAi), the count does not stop and the TSTARTi bit remains unchanged even if 0 (count

stops) is written to the TSTARTi bit.

The TSTARTi bit is set to 0 (count stops) only by a compare match with the TRDGRAi register.

If the CSELi bit is 0 when rewriting the TRDSTR register, write 0 to the TSTARTi bit to change the CSELi bit to 1

without affecting count operation.

If 1 is written to the TSTARTi bit while the counter is stopped, count may be started.

To stop counting by a program, set the TSTARTi bit after setting the CSELi bit to 1. Even if 1 is written to the

CSELi bit and 0 is written to the TSTARTi bit at the same time (using one instruction), the count cannot be

stopped.

Table 8-21 lists the TRDIOji (j = A, B, C, or D) Pin Output Level When Count Stops while using the TRDIOji (j = A,

B, C, or D) pin for timer RD output.

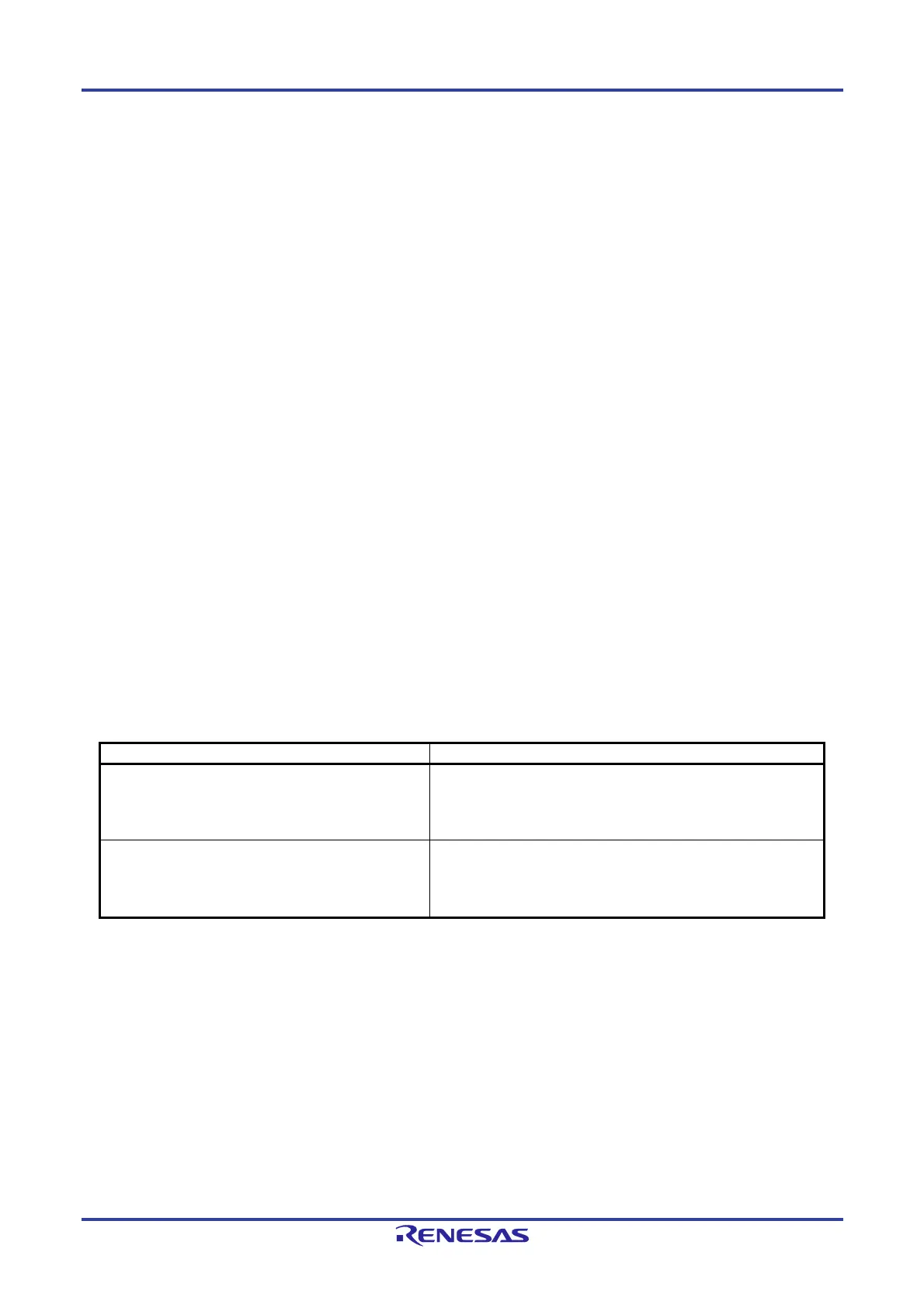

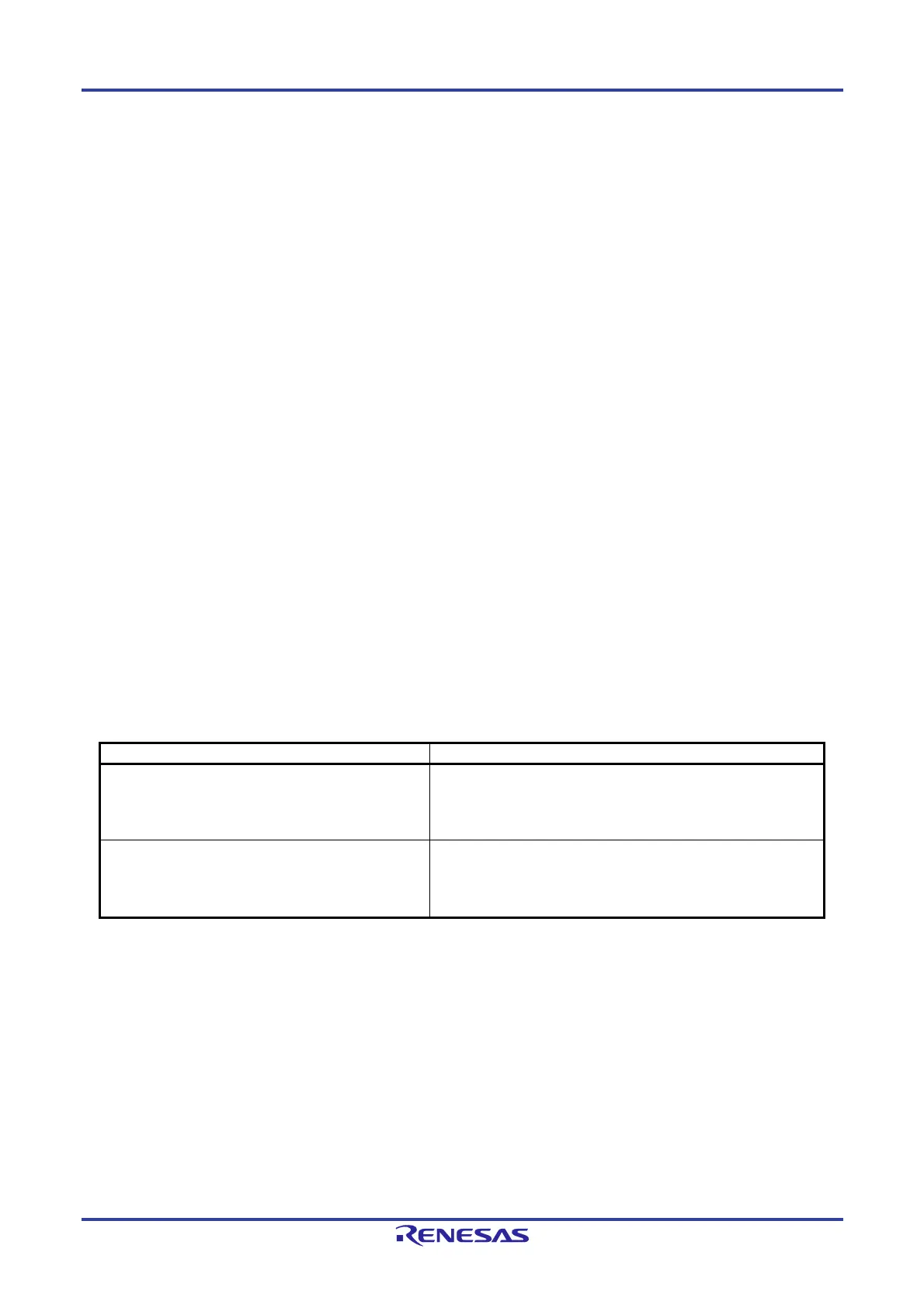

Table 8-21. TRDIOji (j = A, B, C, or D) Pin Output Level When Count Stops

Count Stop TRDIOji Pin Output When Count Stops

When the CSELi bit is set to 1, write 0 to the

TSTARTi bit and the count stops.

The pin holds the output level immediately before the count stops.

(The pin outputs the initial output level selected by bits OLS0 and

OLS1 in the TRDFCR register in timer RD complementary and reset

synchronous PWM modes.)

When the CSELi bit is set to 0, the count stops at

compare match with registers TRDi and TRDGRAi.

The pin holds the output level after the output changes by compare

match. (The pin outputs the initial output level selected by bits OLS0

and OLS1 in the TRDFCR register in timer RD complementary and

reset synchronous PWM modes.)

Remark i = 0 or 1, j = A, B, C, or D

(2) TRDDFi Register (i = 0 or 1)

Set bits DFCK0 and DFCK1 in the TRDDFi register before starting count operation.

8.5.2 Mode Switching

Set the count to stopped (set bits TSTART0 and TSTART1 to 0) before switching modes during operation.

Set bits TRDIF0 and TRDIF1 to 0 before changing bits TSTART0 and TSTART1 from 0 to 1. Refer to CHAPTER 21

INTERRUPT FUNCTIONS for details.

Loading...

Loading...