RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1243

Dec 10, 2015

17.5.5 Error Status

In UART mode, the LIN/UART module can detect four types of errors and two types of statuses. The condition of these error

statuses can be checked by means of the corresponding bits in the LESTn register.

Table 17-27 lists applicable error status types.

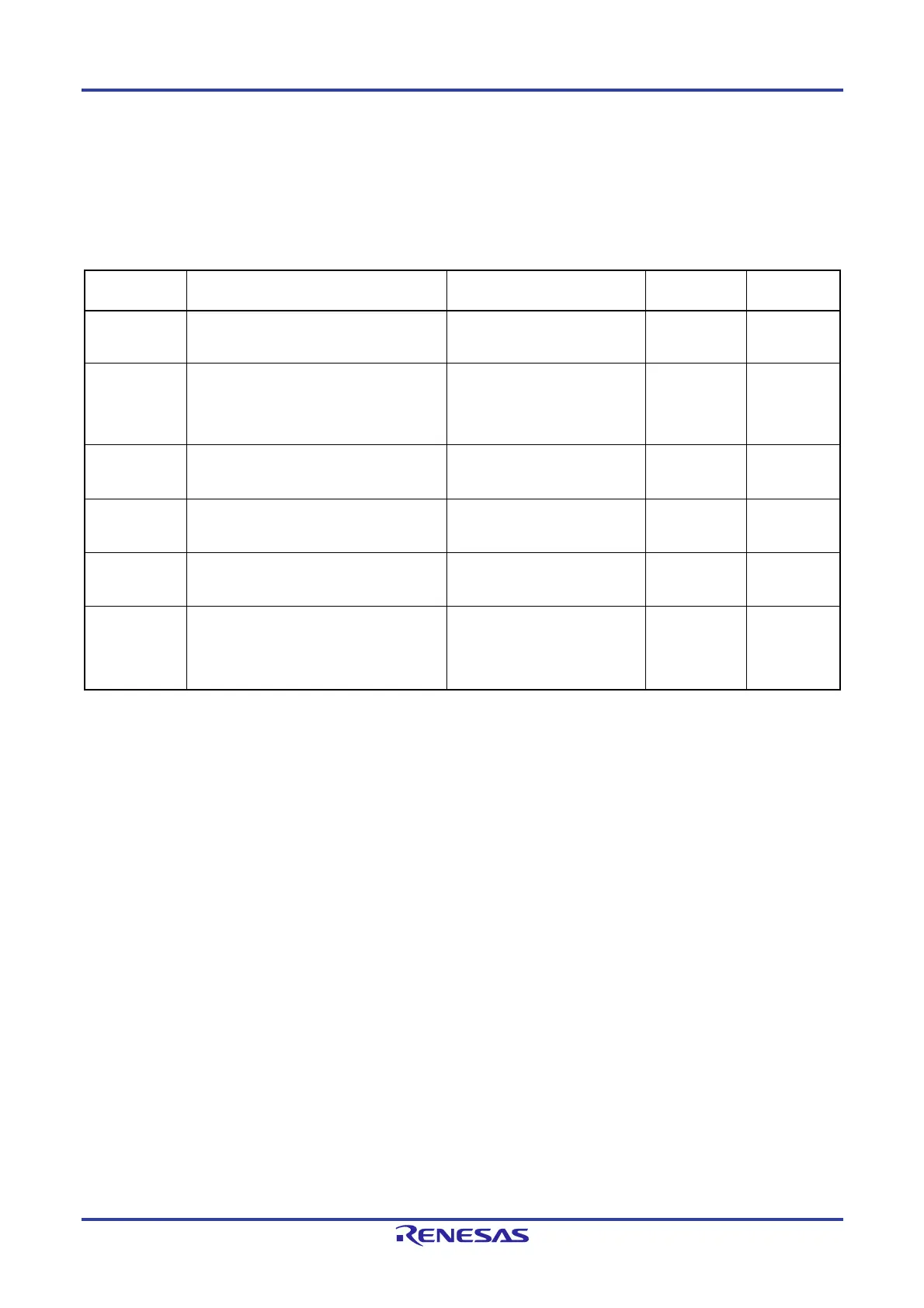

Table 17-27.

Types of Error Statuses in UART Mode

Status Error detection condition Communication

Enable/disable

detection

Corresponding

bit

Bit error The transmitted data and the data monitored

on the receive pin do not match

Note 1

Continues until the

transmission of the set

transmission data is finished.

O BER flag in

LESTn register

Overrun error After received data is stored in the LURDRn

register, another data item is received before

the data is read.

(In this case, no data is stored in the

LURDRn register).

―

(Reception is finished by the

time this error is detected)

O OER flag in

LESTn register

Framing error When the first stop bit at the first bit is low in

the reception processing.

―

(Reception is finished by the

time this error is detected)

O FER flag in

LESTn register

Parity error The received parity value fails to match the

parity value calculated from the received

data

Continues until the data

reception is finished.

×

Note 2

UPER flag in

LESTn register

Expansion bit

detection

The value of the received expansion bit

matches the value of the UEBDL bit in the

LUORn1 register.

― O EXBT flag in

LESTn register

ID match The value of the received expansion bit

matches the value of the UEBDL bit in the

LUORn1 register and the 8-bit received data

excluding the expansion bit matches the

value of the LIDBn register.

― O IDMT flag in

LESTn register

Notes 1. If data is transmitted from the UART buffer, a bit error is also detected in the space between UART frames

(inter-byte space).

2. Setting the UPS[1:0] bits in the LBFCn register to 10b (0 parity) disables the checking of parity bit values. In

this case, no parity error is generated.

Caution The error status is cleared when cleared by software or after transition to LIN reset mode.

Loading...

Loading...