RL78/F13, F14 CHAPTER 8 TIMER RD

R01UH0368EJ0210 Rev.2.10 647

Dec 10, 2015

8.4 Timer RD Interrupt

Timer RD generates the timer RDi (i = 0 or 1) interrupt request from six sources for each timer RD0 and timer RD1.

Table 8-20 lists the Registers Associated with Timer RD Interrupt and Figure 8-62 shows the Timer RD Interrupt Block

Diagram.

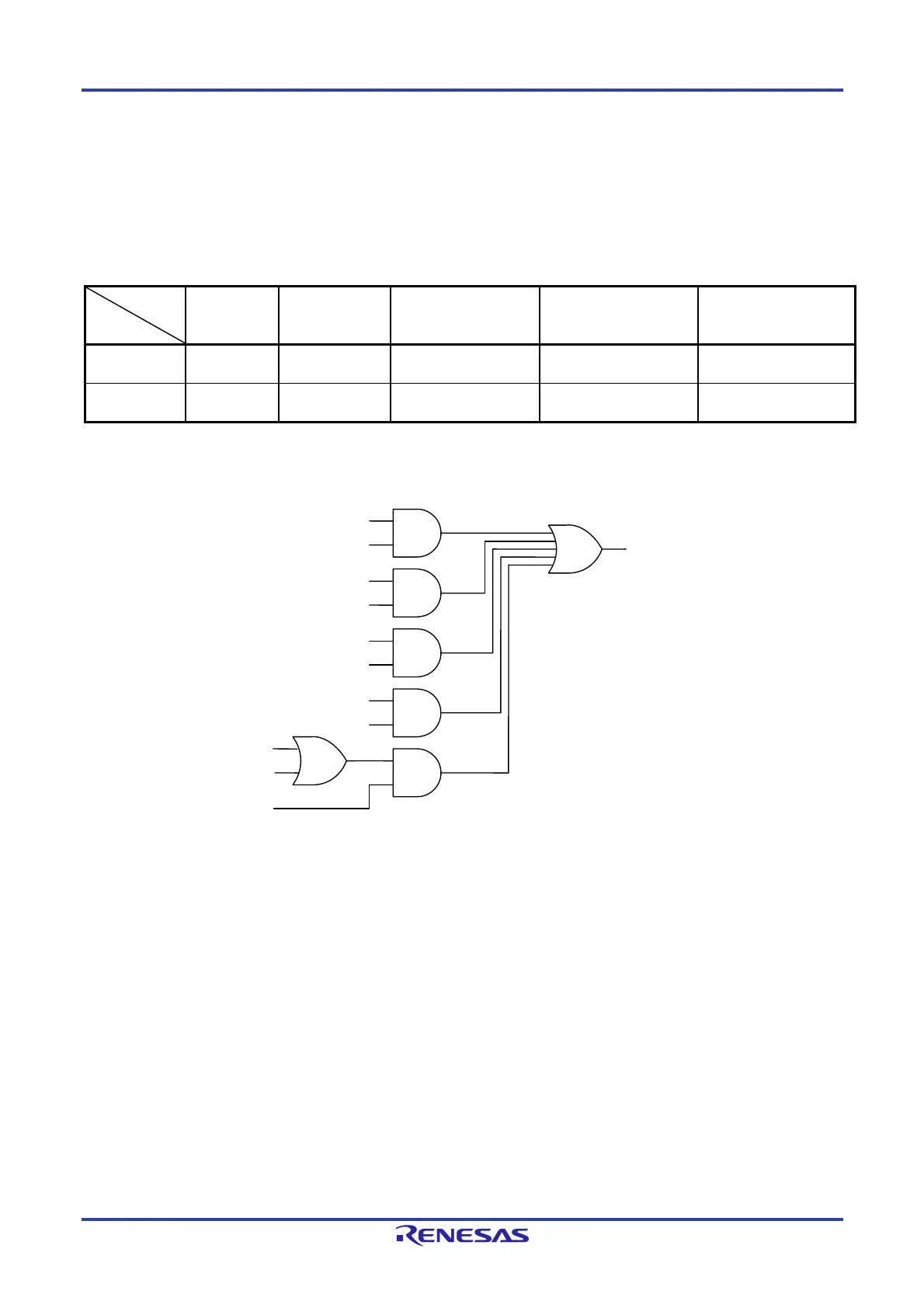

Table 8-20. Registers Associated with Timer RD Interrupt

Timer RD

Status

Register

Timer RD

Interrupt Enable

Register

Interrupt Request Flag

(Register)

Interrupt Mask Flag

(Register)

Priority Specification Flag

(Register)

Timer RD0

TRDSR0 TRDIER0 TRDIF0 (IF0H) TRDMK0 (MK0H) TRDPR00 (PR00H)

TRDPR10 (PR10H)

Timer RD1

TRDSR1 TRDIER1 TRDIF1 (IF0H) TRDMK1 (MK0H) TRDPR01 (PR00H)

TRDPR11 (PR10H)

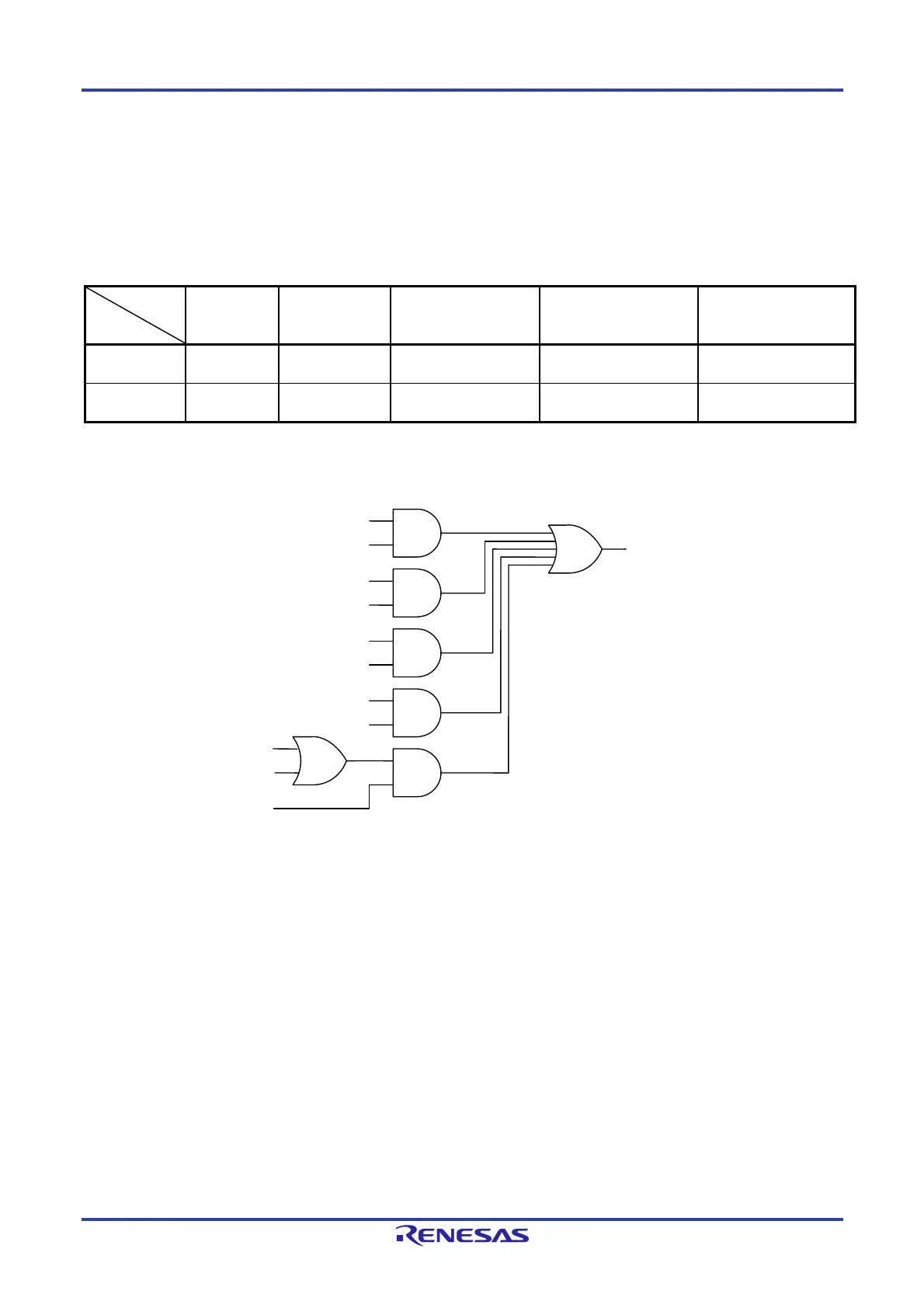

Figure 8-62. Timer RD Interrupt Block Diagram

Since the interrupt source (timer RD interrupt) is generated by a combination of multiple interrupt request sources for

timer RD, the following differences from other maskable interrupts apply:

When a bit in the TRDSRi register is 1 and the corresponding bit in the TRDIERi register is 1 (interrupt enabled),

the TRDIFi bit in the IF0H register is set to 1 (interrupt requested).

If multiple bits in the TRDIERi register are set to 1, use the TRDSRi register to determine the source of the interrupt

request.

Since the bits in the TRDSRi register are not automatically set to 0 even if the interrupt is acknowledged, set the

corresponding bit to 0 in the interrupt routine.

Use either (a) or (b) described below to clear each bit of the TRDSRi register.

(a) Set the TRDIERi register to 00H (disabling all interrupts) and then write 0 to all of the status flags.

(b) When at least one bit in the TRDIERi register has the setting 1 and the status flag of an interrupt source

enabled by the corresponding bit is 1, write 0 to all of the status flag bits whose settings are 1 in the TRDSRi

register.

Timer RDi

interrupt request

Timer RDi

IMFA bit

IMIEA bit

IMFB bit

IMIEB bit

IMFC bit

IMIEC bit

UDF bit

OVF bit

OVIE bit

i = 0 to 1

IMFA, IMFB, IMFC, IMFD, OVF, UDF : TRDSRi register bit

IMIEA, IMIEB, IMIEC, IMIED, OVIE : TRDIERi register bit

IMFD bit

IMIED bit

Loading...

Loading...