RL78/F13, F14 CHAPTER 7 TIMER RJ

R01UH0368EJ0210 Rev.2.10 546

Dec 10, 2015

7.3.1 Peripheral enable register 1 (PER1)

The PER1 register is used to enable or disable supplying the clock to the peripheral hardware. Clock supply to the

hardware that is not used is also stopped so as to decrease the power consumption and noise.

To use Timer RJ, be sure to set bit 0 (TRJ0EN) to 1.

Set the PER1 register by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

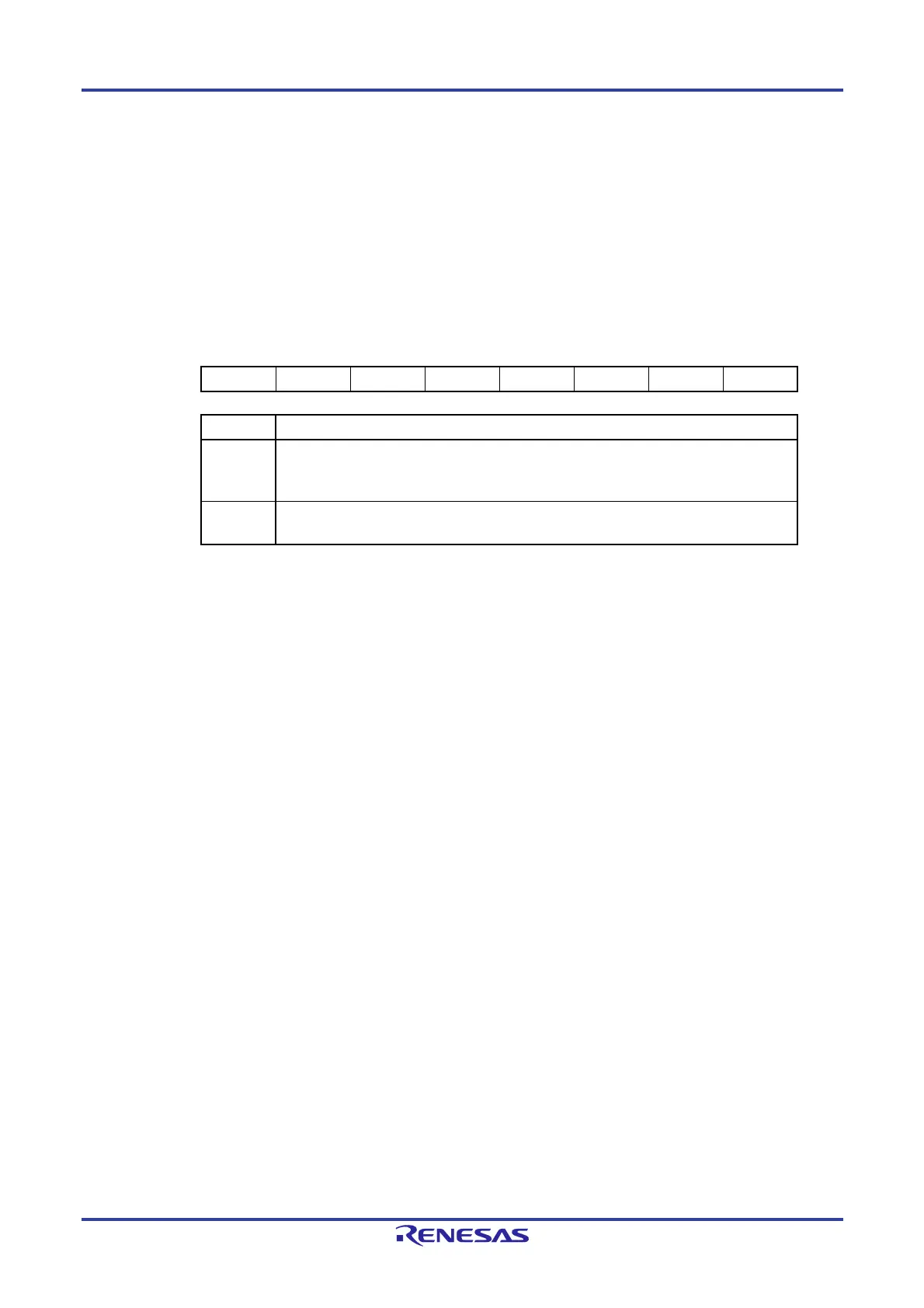

Figure 7-2. Format of Peripheral Enable Register 1 (PER1)

Address: F02C0H After reset: 00H R/W

Symbol <7> <6> <5> <4> <3> 2 1 <0>

PER1 DACEN

Note

0 CMPEN

Note

TRD0EN DTCEN 0 0 TRJ0EN

TRJ0EN Control of timer RJ0 input clock supply

0

Stops input clock supply.

SFR used by timer RJ0 cannot be written.

Timer RJ0 is in the reset status.

1

Enables input clock supply.

SFR used by timer RJ0 can be read and written.

Note Only on the RL78/F14.

Cautions 1. When setting timer RJ, be sure to set the TRJ0EN bit to 1 first. If TRJ0EN = 0, writing

to a control register of timer RJ is ignored, and all read values are default values

(except for port mode registers 1, 4 (PM1, PM4) and port registers 1, 4 (P1, P4)).

2. Be sure to set the following bits to 0:

RL78/F13: bits 1, 2, 5, 6, and 7

RL78/F14: bits 1, 2, and 6

Loading...

Loading...