RL78/F13, F14 CHAPTER 6 TIMER ARRAY UNIT

R01UH0368EJ0210 Rev.2.10 471

Dec 10, 2015

6.5 Operation Timing of Counter

6.5.1 Count clock (f

TCLK)

The count clock (fTCLK) of the timer array unit can be selected between following by CCSmn bit of timer mode register mn

(TMRmn).

Operation clock (f

MCK) specified by the CKSmn0 and CKSmn1 bits

Valid edge of input signal input from the TImn pin

Because the timer array unit is designed to operate in synchronization with f

CLK, the timings of the count clock (fTCLK) are

shown below.

(1) When operation clock (fMCK) specified by the CKSmn0 and CKSmn1 bits is selected (CCSmn = 0)

The count clock (f

TCLK) is between fCLK to fCLK /2

15

by setting of timer clock select register m (TPSm). When a divided

f

CLK is selected, however, the clock is a signal which becomes high level for one period of fCLK from its rising edge.

When f

CLK is selected, the clock is fixed high.

Counting of timer count register mn (TCRmn) delayed by one period of f

CLK from rising edge of the count clock,

because of synchronization with f

CLK. But, this is described as “counting at rising edge of the count clock”, as a

matter of convenience.

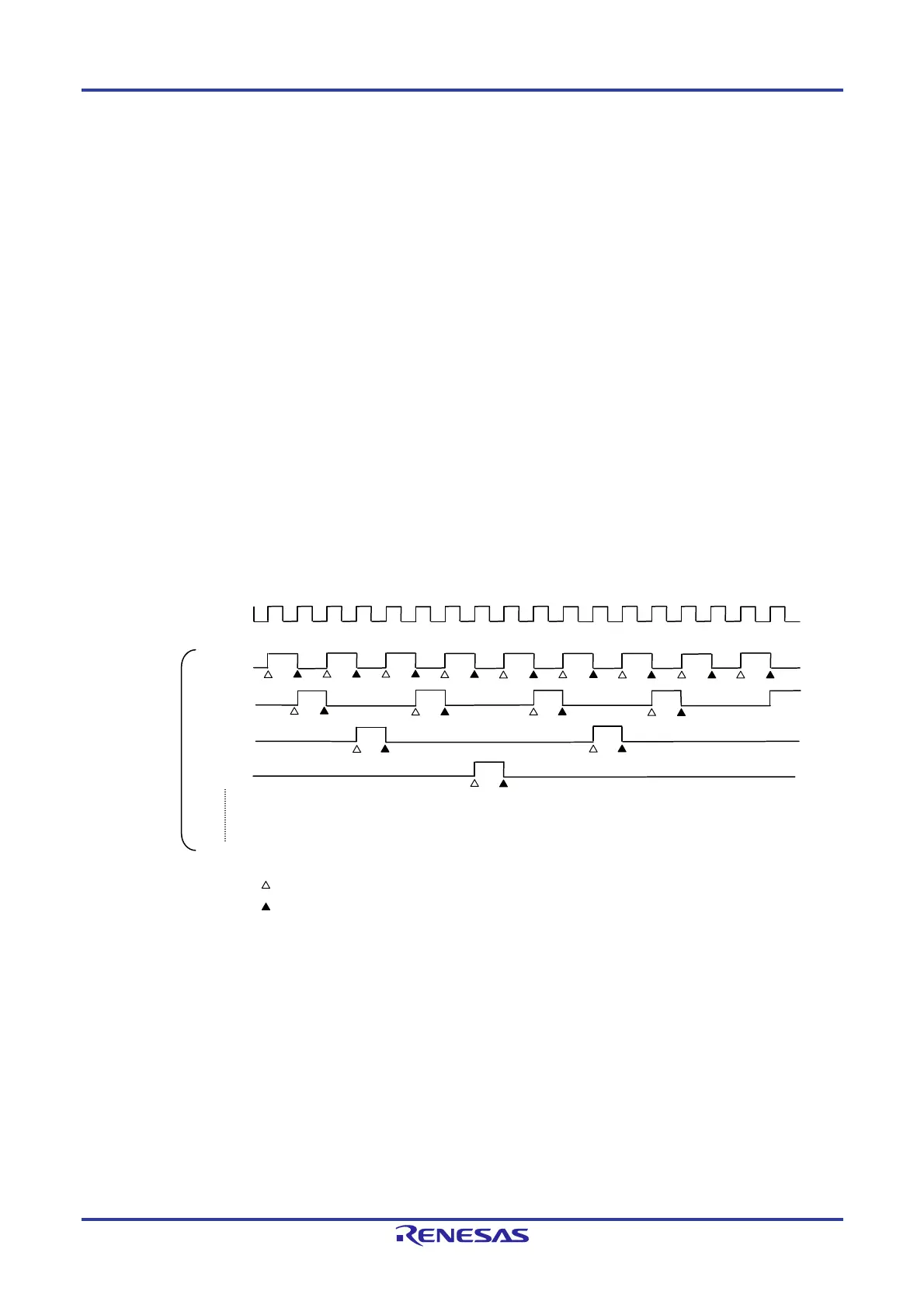

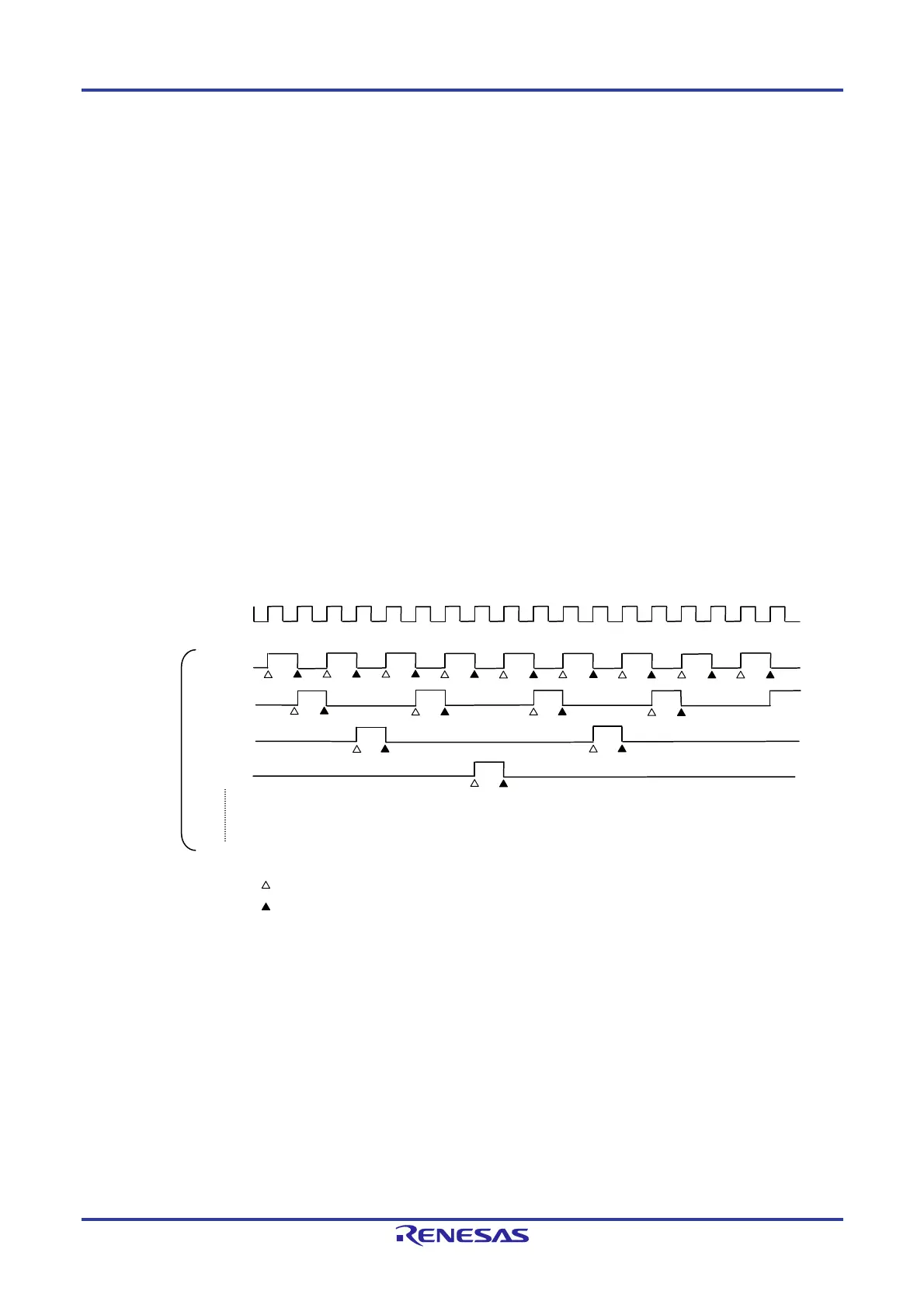

Figure 6-27. Timing of fCLK and count clock (fTCLK) (When CCSmn = 0)

Remarks 1. : Rising edge of the count clock

: Synchronization, increment/decrement of counter

2.

f

CLK

: CPU/peripheral hardware clock

f

CLK

f

TCLK

( = f

MCK

= CKmn)

f

CLK

/2

f

CLK

/4

f

CLK

/8

f

CLK

/16

Loading...

Loading...