RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1224

Dec 10, 2015

17.5 UART Mode

17.5.1 Operation Overview

(1) Transmission

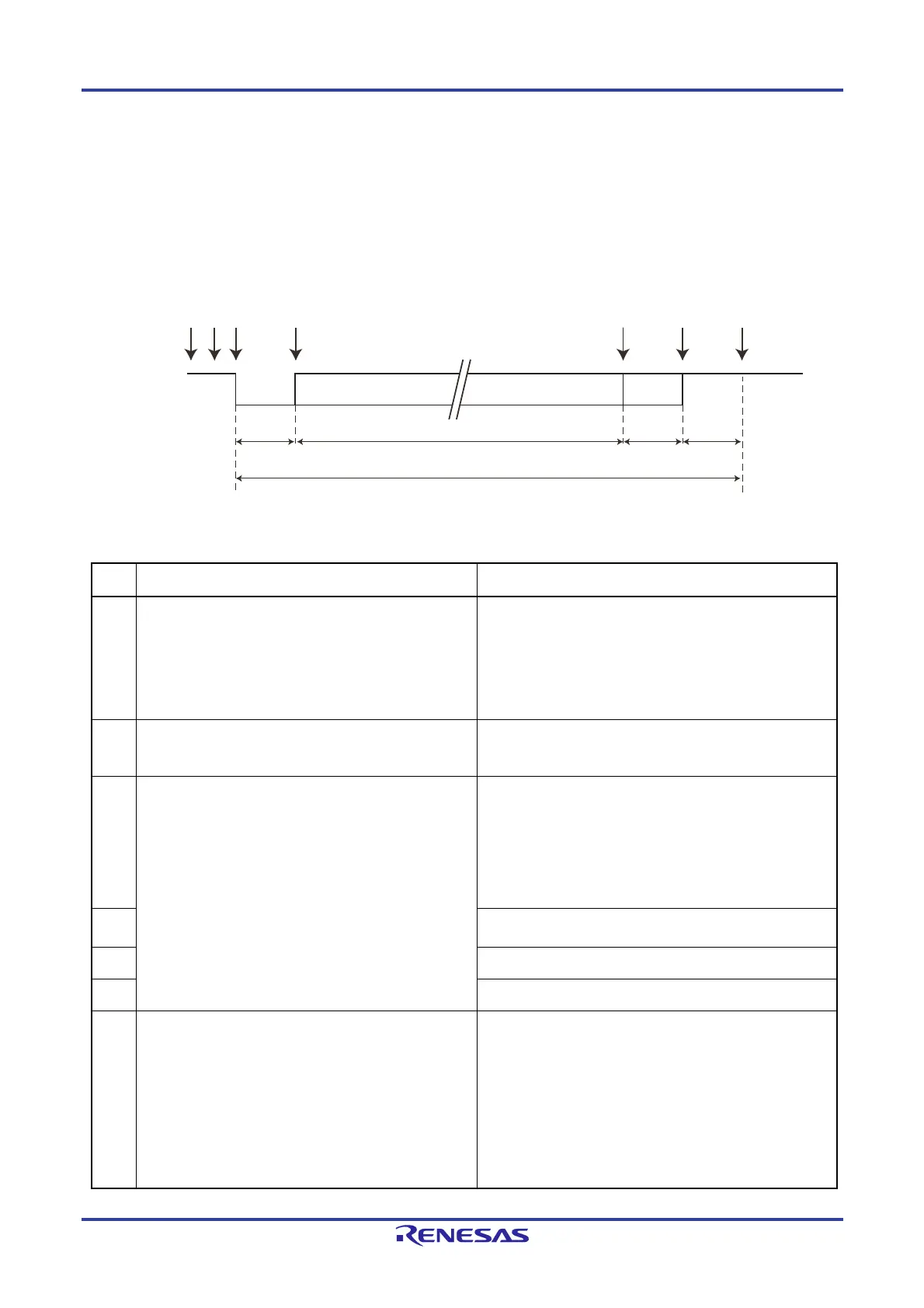

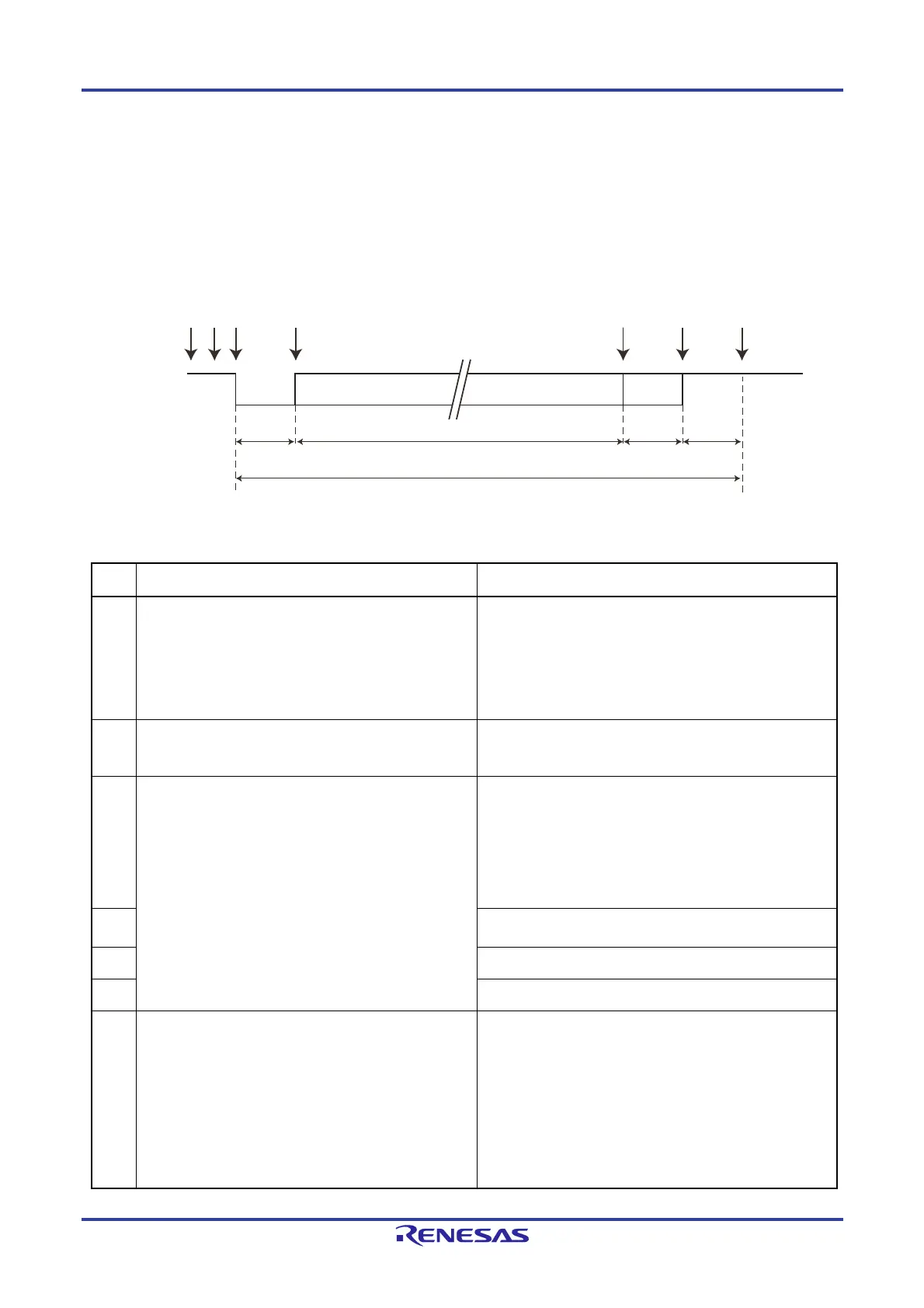

Figure 17-22 shows LIN/UART module (in UART mode) transmission operations; Table 17-18 shows LIN/UART module (in

UART mode) transmission processing.

Figure 17-22. LIN/UART Module (in UART mode) Transmission Operation

Table 17-18. LIN/UART Module (UART Mode) Transmission Processing

Step Software processing LIN/UART module processing

(1)

Sets a baud rate.

Sets noise filter ON/OFF.

Sets error detection enable.

Sets data format

Sets an interrupt generation timing.

Clears the LIN/UART module from LIN reset mode

Sets the transmit enable bit (UTOE bit) to 1

Waits for a transmission trigger (LUTDRn register) by

software.

(2)

Sets the transmission data in the UART transmission

data register (LUTDRn register) or UART wait

transmission data (LUWTDRn).

Sets the transmission status flag.

(3)

Waits for an interrupt request.

[When the UTIGTS bit is 0 (a transmission interrupt request

is output upon start of transmission)]

When transmitting data continuously, sets another piece

of transmission data in the UART transmission data

register (LUTDRn register), waits for the generation of

an interrupt request.

Transmits a start bit (for switching between transmission

and reception in half duplex communication, transmits a

start bit after receiving 1 stop bit. This function is referred to

in 17.5.1 (4) Transmission Start Wait Function).

[When the UTIGTS bit is 0 (a transmission interrupt request is

output upon start of transmission)]

Outputs a transmission interrupt.

(4) Transmits the data set in the UART (wait) transmission data

register.

(5) Transmits a parity bit when parity is used.

(6) Transmits 1 or 2 stop bits.

(7) [When the UTIGTS bit is 0 (a transmission interrupt request

is output upon start of transmission)]

If another piece of transmission data is set, goes to step

(3).

[When the UTIGTS bit is 1 (a transmission interrupt request

is output upon end of transmission)]

When transmitting data continuously, goes to step (2).

[When the UTIGTS bit is 0 (a transmission interrupt request is

output upon start of transmission)]

If another piece of transmission data is set, goes to step

(3).

If another piece of transmission data is not set, clears the

transmission status flag.

[When the UTIGTS bit is 1 (a transmission interrupt request is

output upon end of transmission)]

Outputs a transmission interrupt.

Clears the transmission status flag

Idle

1 or 2

stop bits

0 or 1

parity bit

7, 8, or 9 data bits

UART frame

Idle

LTXDn

n = 0, 1

(1) (4)(3) (5) (6) (7)(2)

Start bit

Loading...

Loading...