RL78/F13, F14 CHAPTER 15 SERIAL ARRAY UNIT

R01UH0368EJ0210 Rev.2.10 1015

Dec 10, 2015

15.9.6 Procedure for processing errors that occurred during simplified I

2

C (IIC00, IIC01, IIC10, IIC11) communication

The procedure for processing errors that occurred during simplified I

2

C (IIC00, IIC01, IIC10, IIC11) communication is

described in Figure 15-155 and 15-156.

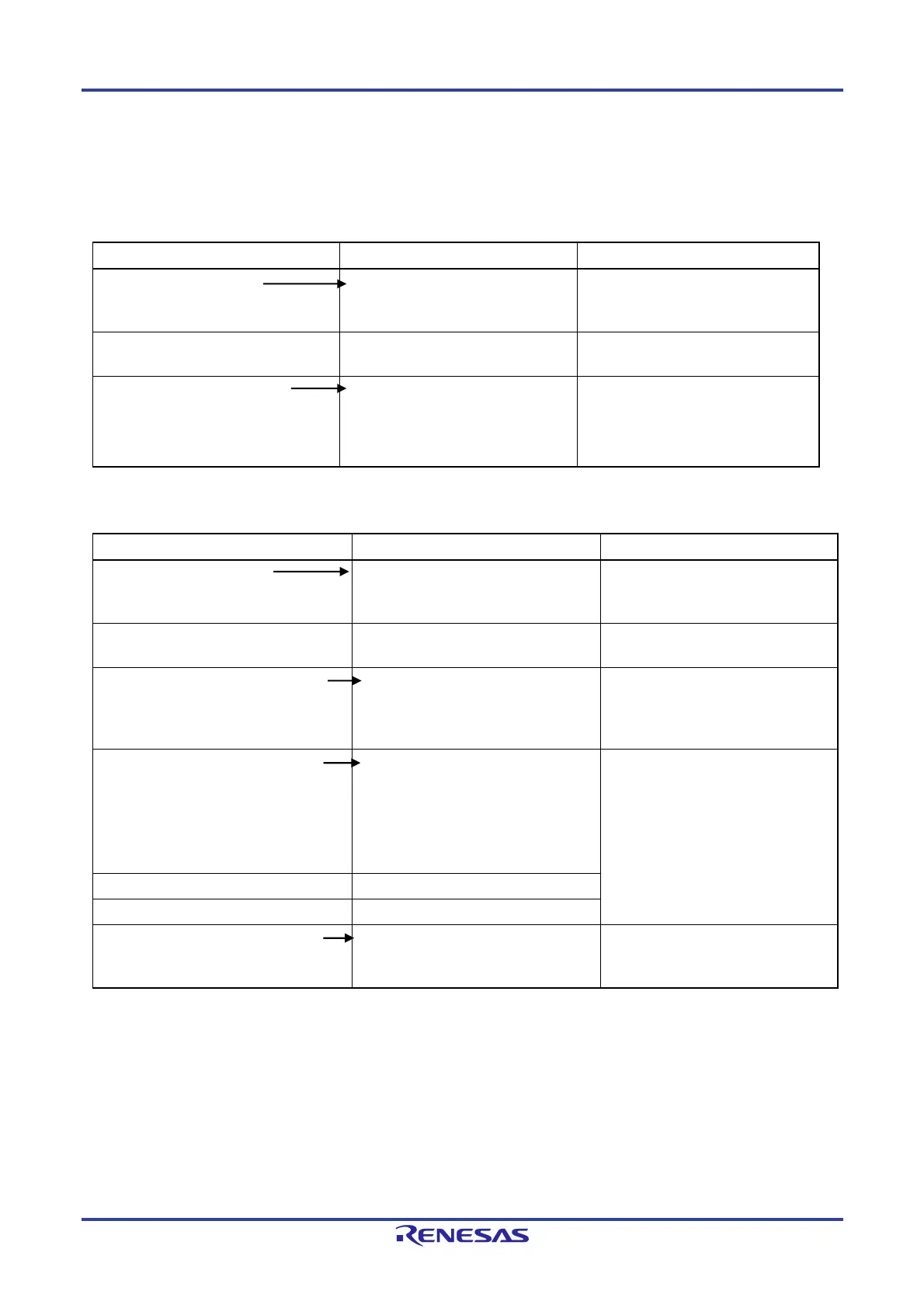

Figure 15-155. Processing Procedure in Case of Overrun Error

Software Manipulation Hardware Status Remark

Reads serial data register mn

(SDRmn).

The BFFmn bit of the SSRmn register

is set to 0 and channel n is enabled to

receive data.

This is to prevent an overrun error if the

next reception is completed during error

processing.

Reads serial status register mn

(SSRmn).

Error type is identified and the read

value is used to clear error flag.

Writes 1 to serial flag clear trigger

register mn (SIRmn).

Error flag is cleared. Error can be cleared only during

reading, by writing the value read from

the SSRmn register to the SIRmn

register without modification.

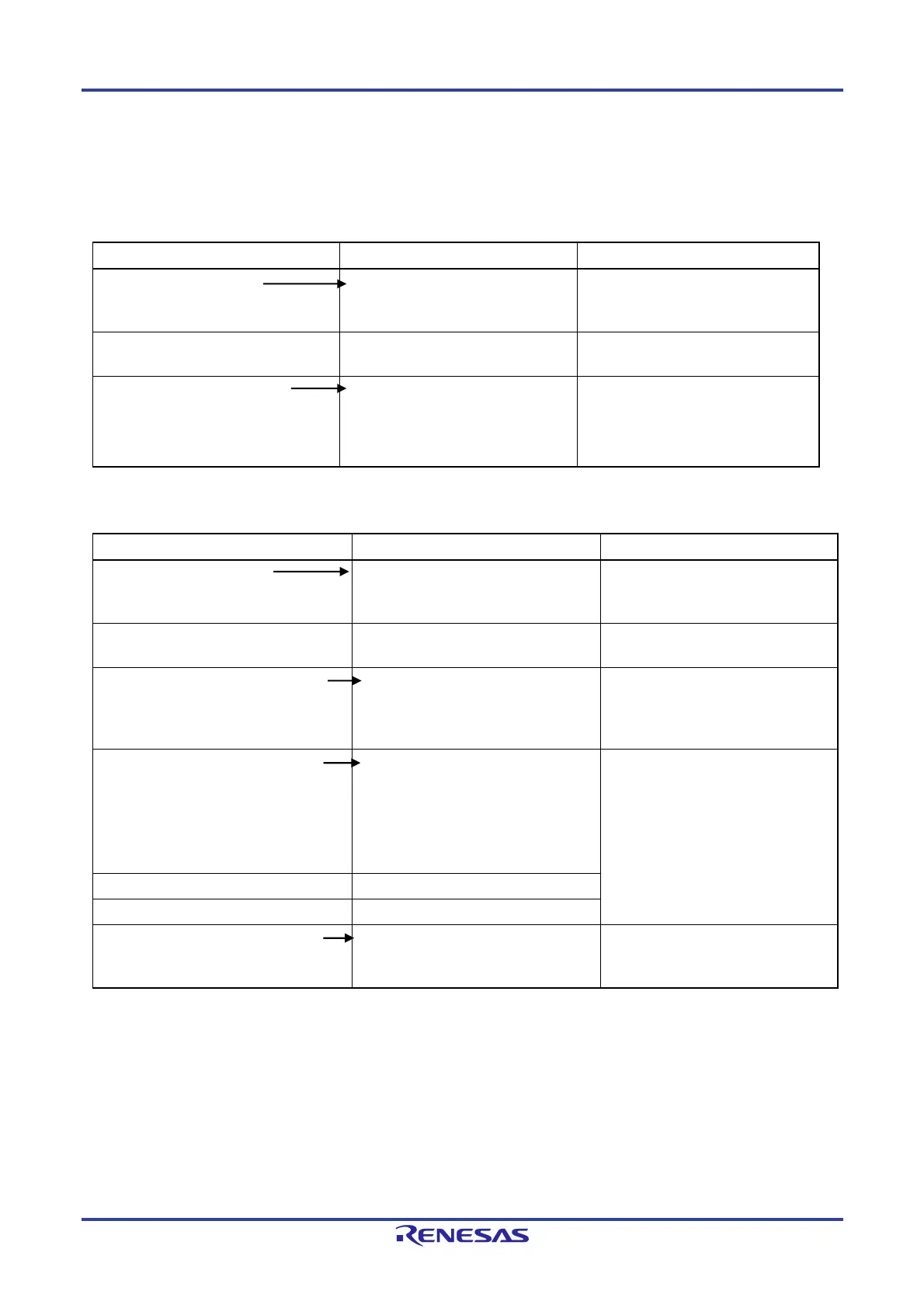

Figure 15-156. Processing Procedure in Case of Parity Error (ACK error) in Simplified I

2

C Mode

Software Manipulation Hardware Status Remark

Reads serial data register mn

(SDRmn).

The BFFmn bit of the SSRmn register is

set to 0 and channel n is enabled to

receive data.

This is to prevent an overrun error if the

next reception is completed during

error processing.

Reads serial status register mn (SSRmn). Error type is identified and the read

value is used to clear error flag.

Writes serial flag clear trigger register mn

(SIRmn).

Error flag is cleared. Error can be cleared only during

reading, by writing the value read from

the SSRmn register to the SIRmn

register without modification.

Sets the STmn bit of serial channel stop

register m (STm) to 1.

The SEmn bit of serial channel enable

status register m (SEm) is set to 0 and

channel n stops operation.

Slave is not ready for reception

because ACK is not returned.

Therefore, a stop condition is created,

the bus is released, and

communication is started again from

the start condition. Or, a restart

condition is generated and

transmission can be redone from

address transmission.

Creates stop condition.

Creates start condition.

Sets the SSmn bit of serial channel start

register m (SSm) to 1.

The SEmn bit of serial channel enable

status register m (SEm) is set to 1 and

channel n is enabled to operate.

Remark m: Unit number (m = 0, 1), n: Channel number (n = 0, 1), r: IIC number (r = 00, 01, 10, 11)

mn = 00, 01, 10, 11

Loading...

Loading...