RL78/F13, F14 CHAPTER 27 SAFETY FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1612

Dec 10, 2015

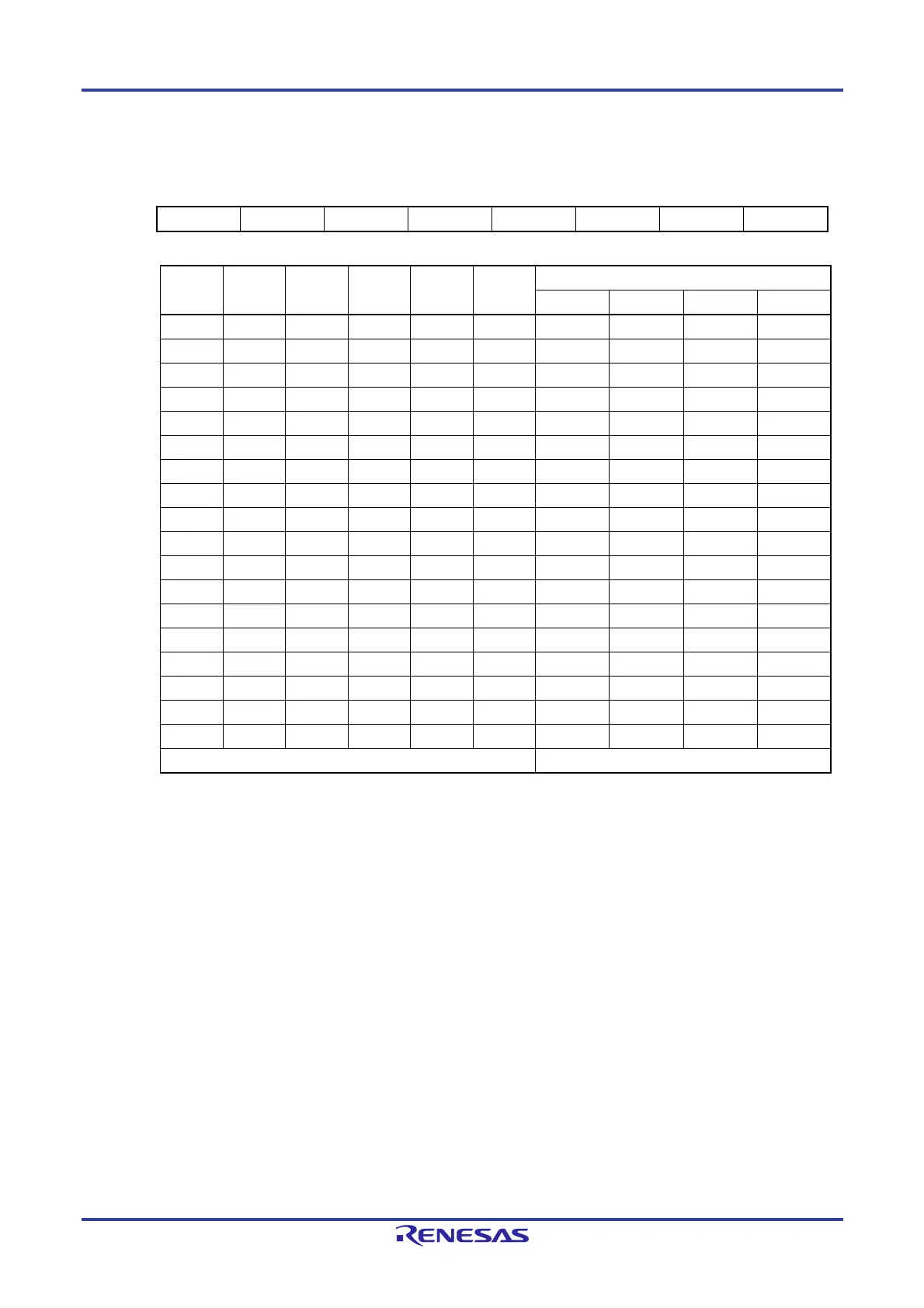

Figure 27-27. Format of Analog Input Channel Specification Register (ADS) (2/2)

Address: FFF31H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

ADS ADISS 0 0 ADS4 ADS3 ADS2 ADS1 ADS0

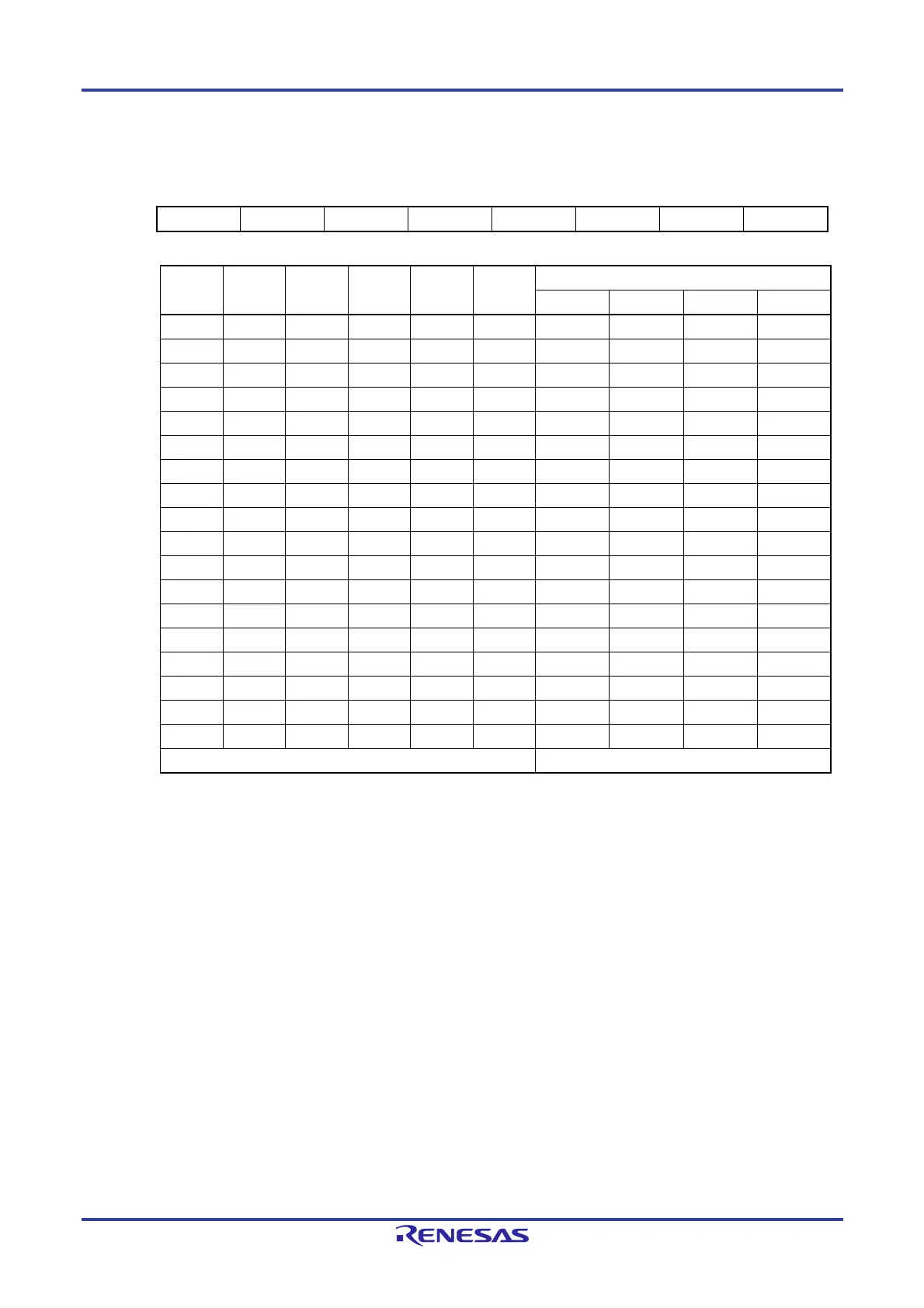

Scan mode (ADMD = 1)

ADISS ADS4 ADS3 ADS2 ADS1 ADS0 Analog input channel

Scan 0 Scan 1 Scan 2 Scan 3

0 0 0 0 0 0 ANI0 ANI1 ANI2 ANI3

0 0 0 0 0 1 ANI1 ANI2 ANI3 ANI4

0 0 0 0 1 0 ANI2 ANI3 ANI4 ANI5

0 0 0 0 1 1 ANI3 ANI4 ANI5 ANI6

0 0 0 1 0 0 ANI4 ANI5 ANI6 ANI7

0 0 0 1 0 1 ANI5 ANI6 ANI7 ANI8

0 0 0 1 1 0 ANI6 ANI7 ANI8 ANI9

0 0 0 1 1 1 ANI7 ANI8 ANI9 ANI10

0 0 1 0 0 0 ANI8 ANI9 ANI10 ANI11

0 0 1 0 0 1 ANI9 ANI10 ANI11 ANI12

0 0 1 0 1 0 ANI10 ANI11 ANI12 ANI13

0 0 1 0 1 1 ANI11 ANI12 ANI13 ANI14

0 0 1 1 0 0 ANI12 ANI13 ANI14 ANI15

0 1 0 0 0 0 ANI16 ANI17 ANI18 ANI19

0 1 0 0 0 1 ANI17 ANI18 ANI19 ANI20

0 1 0 0 1 0 ANI18 ANI19 ANI20 ANI21

0 1 0 0 1 1 ANI19 ANI20 ANI21 ANI22

0 1 0 1 0 0 ANI20 ANI21 ANI22 ANI23

Other than the above Setting prohibited

Cautions

1. Be sure to clear bits 5 and 6 to 0.

2. In port mode registers 3, 7 to 10, and 12 (PM3, PM7 to PM10, PM12), set the ADPC and

PMCxx registers to the input mode for pins to be set as analog inputs.

3. In the ADS register, do not select a pin which is set as a digital I/O pin in the A/D port

configuration register (ADPC).

4. In the ADS register, do not select a pin which is set as a digital I/O pin in the port mode

control register 7, 9, 12 (PMC7, PMC9, PMC12)

5. Only rewrite the value of the ADISS bit while A/D voltage comparator operation is stopped

(which is indicated by the ADCE bit of A/D converter mode register 0 (ADM0) being 0).

6. If using AV

REFP as the + side reference voltage source of the A/D converter, do not select

ANI0 as an A/D conversion channel.

7. If using AV

REFM as the - side reference voltage source of the A/D converter, do not select

ANI1 as an A/D conversion channel.

8. If ADISS is set to 1, the internal reference voltage (1.45 V) cannot be used for the + side

reference voltage source.

9. When the CPU enters the STOP mode or HALT mode while being driven by the

subsystem/low-speed on-chip oscillator select clock, do not set the ADISS bit to 1. Setting

ADISS to 1 increases the value given in 34.3.2 Supply Current Characteristics or 35.3.2

Supply Current Characteristics.

10. Ignore the result of conversion if the corresponding ANI pin is not present.

Loading...

Loading...