RL78/F13, F14 CHAPTER 8 TIMER RD

R01UH0368EJ0210 Rev.2.10 641

Dec 10, 2015

Table 8-18. Complementary PWM Mode Specifications

Item Specification

Count sources

Note 1

fCLK, fPLL, fIH, fSUB, fIL

External signal input to the TRDCLK0 pin (active edge selected by a program)

Set bits TCK2 to TCK0 in the TRDCR1 register to the same value (same count source)

as bits TCK2 to TCK0 in the TRDCR0 register.

Count operations Increment or decrement.

Registers TRD0 and TRD1 are decremented with the compare match with registers

TRD0 and TRDGRA0 during increment operation. When the TRD1 register changes

from 0000H to FFFFH during decrement operation, and registers TRD0 and TRD1 are

incremented.

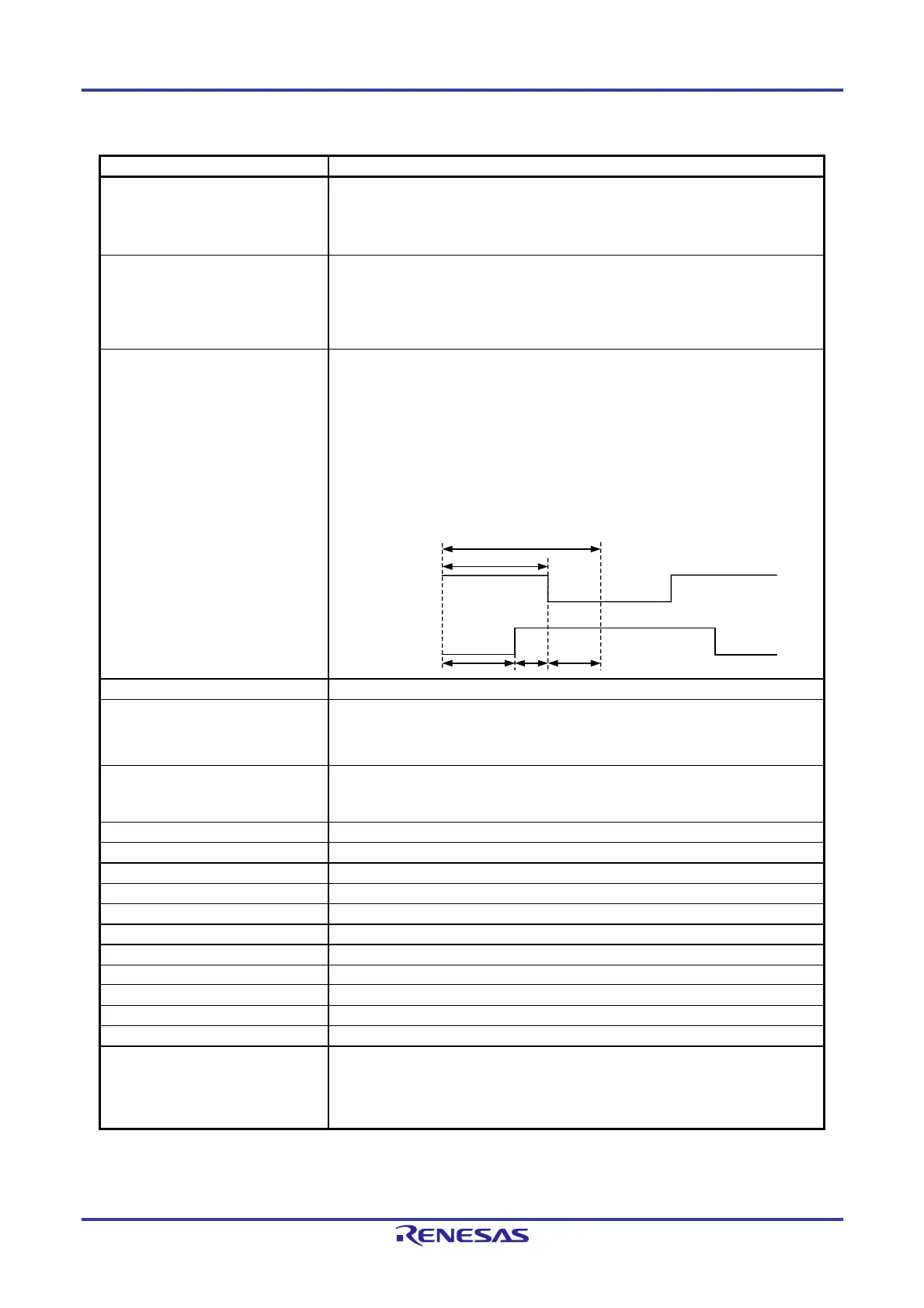

PWM waveform

PWM period: 1/fk × (m + 2 - p) × 2

Note 2

Dead time: p

Active level width of normal-phase: 1/fk × (m - n - p + 1) × 2

Active level width of counter-phase: 1/fk × (n + 1 - p) × 2

fk: Frequency of count source

m: Value set in the TRDGRA0 register

n: Value set in the TRDGRB0 register (PWM1 output)

Value set in the TRDGRA1 register (PWM2 output)

Value set in the TRDGRB1 register (PWM3 output)

p: Value set in the TRD0 register

Count start condition 1 (count starts) is written to bits TSTART0 and TSTART1 in the TRDSTR register.

Count stop condition 0 (count stops) is written to bits TSTART0 and TSTART1 in the TRDSTR register when

the CSEL0 bit in the TRDSTR register is set to 1. (The PWM output pin outputs the

initial output level selected by bits OLS0 and OLS1 in the TRDFCR register.)

Interrupt request generation timing • Compare match (content of the TRDi register matches content of the TRDGRji

register)

• TRD1 register underflow

TRDIOA0 pin function I/O port or TRDCLK (external clock) input

TRDIOB0 pin function PWM1 output normal-phase output

TRDIOD0 pin function PWM1 output counter-phase output

TRDIOA1 pin function PWM2 output normal-phase output

TRDIOC1 pin function PWM2 output counter-phase output

TRDIOB1 pin function PWM3 output normal-phase output

TRDIOD1 pin function PWM3 output counter-phase output

TRDIOC0 pin function Output inverted every 1/2 period of PWM

INTP0 pin function Pulse output forced cutoff signal input (port or INTP0 interrupt input)

Read from timer The count value can be read by reading the TRDi register.

Write to timer The value can be written to the TRDi register.

Selectable functions • Pulse output forced cutoff signal input (see 8. 3. 1 (4) Pulse Output Forced Cutoff)

• The normal-phase and counter-phase active level and initial output level are selected

individually.

• Transfer timing from the buffer register selection

Notes 1. When selecting the count source for the timer RD, set the same clock source as the count source for fCLK

before setting bit 4 (TRD0EN) in the peripheral enable register 1 (PER1).

2. After a count starts, the PWM period is fixed.

Remark i = 0 or 1, j = A, B, C, or D

n + 1

m + 2 - p

n + 1 - p

p m - p - n + 1

Normal-phase

Counter-phase

(When low is selected as the active level )

Loading...

Loading...