A-D Converter

M30240 Group

Rev.1.00 Sep 24, 2003 Page 99 of 360

1.2.24 A-D Converter

The A-D converter consists of one 10-bit successive approximation A-D converter circuit with a

capacitive coupling amplifier. Pins P10

0

to P10

7

function as the analog signal input pins. The direction

registers of these pins for A-D conversion must therefore be set to input. The Vref connect bit (bit 5 at

address 03D7

16

) can be used to isolate the resistance ladder of the A-D converter from the reference

voltage input pin (V

REF

) when the A-D converter is not used. Doing so stops any current flowing into the

resistance ladder from V

REF

, reducing the power dissipation. When using the A-D converter, start A-D

conversion only after setting bit 5 of 03D7

16

to connect V

REF

.

The result of A-D conversion is stored in the A-D registers of the selected pins. When set to 10-bit

precision, the low 8 bits are stored in the even addresses and the high 2 bits in the odd addresses. When

set to 8-bit precision, the low 8 bits are stored in the even addresses.

Table 1.30 shows the performance of the A-D converter. Figure 1.96 shows the block diagram of the A-

D converter, and Figure 1.97 and Figure 1.98 show the A-D converter-related registers.

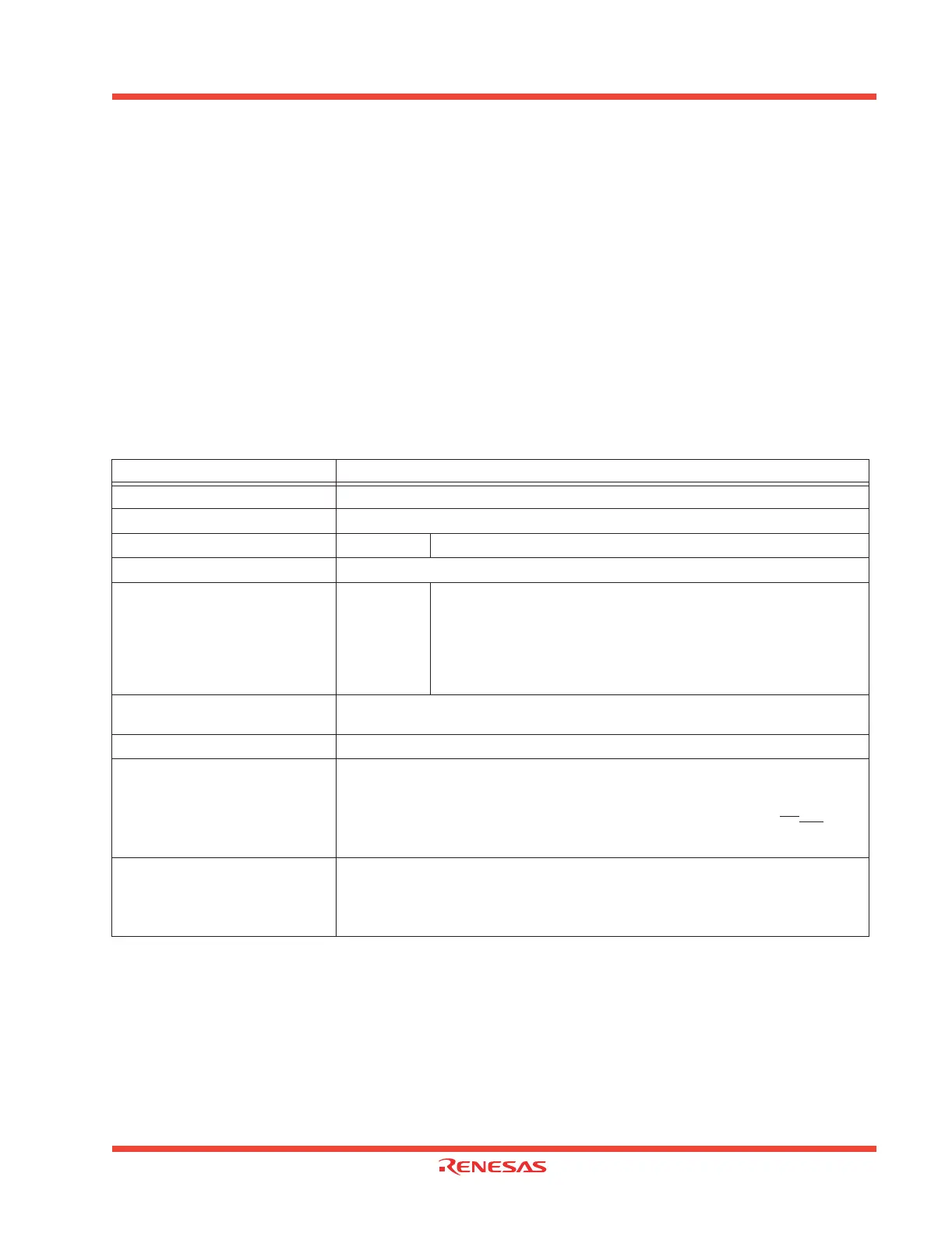

Table 1.30: Performance of A-D Converter

a

a.

Item Performance

Method of A-D conversion Successive approximation (capacitive coupling amplifier)

Analog input voltage (Note) 0V to AV

CC

(V

CC

)

Operating clock fAD V

CC

= 5V f

AD

/divide-by-2 or f

AD

/divide-by-4 or f

AD

, f

AD

,f(X

IN

)

Resolution 8-bit or 10-bit (selectable)

Absolute precision

V

CC

= 5V

• Without sample and hold function

±3LSB

• With sample and hold function (8-bit resolution)

±2LSB

• With sample and hold function (10-bit resolution)

3LSB

Operating modes

One-shot mode, repeat mode, single sweep mode, repeat sweep mode 0, and

repeat sweep mode 1

Analog input pins 8pins (AN

0

to AN

7

)

A-D conversion start condition

•Software trigger

A-D conversion starts when the A-D conversion start flag changes to “1”

•External trigger (can be re-triggered)

A-D conversion starts when the A-D conversion start flag is “1” and the AD

TRG

/P87

input changes from “H” to “L”

Conversion speed per pin

•Without sample and hold function

8-bit resolution: 49

φAD cycles, 10-bit resolution: 59 φAD cycles

• With sample and hold function

8-bit resolution: 28 φAD cycles, 10-bit resolution: 33 φAD cycles

Note: Does not depend on use of sample and hold function

Loading...

Loading...