DMAC

M30240 Group

Rev.1.00 Sep 24, 2003 Page 259 of 360

2.7.2 Operation

2.7.2.1 One-shot transfer mode

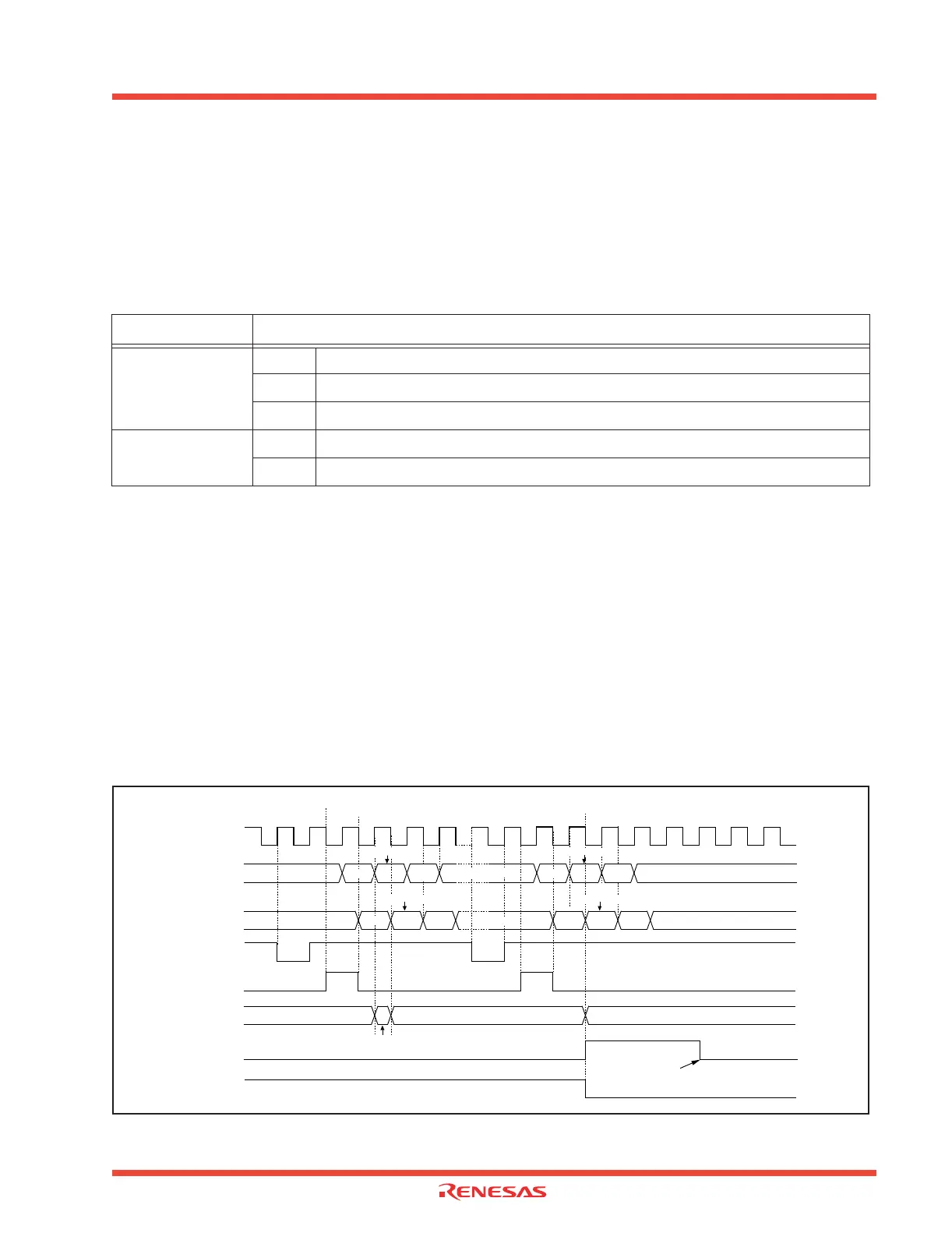

In one-shot transfer mode, select functions from the items shown in Table 2.37. An example using the

indicated options is described below. Figure 2.103 shows an example of operation and Figure 2.104

shows the set-up procedure.

Table 2.39: DMAC in one-shot transfer mode functions

Operation

(1) When a software trigger is selected, setting the software DMA request bit to “1” generates a DMA

transfer request signal.

(2) If DMAC is active, data transfer starts, and the contents of the address indicated by the DMAi for-

ward-direction address pointer are transferred to the address indicated by the DMAi destination point-

er. When data transfer starts directly after DMAC becomes active, the value of the DMAi transfer

counter reload register is reloaded to the DMAi transfer counter, and the value of the DMAi source

pointer is reloaded by the DMAi forward-direction address pointer. Each time a DMA transfer request

signal is generated, 1 byte of data is transferred. The DMAi transfer counter is decremented, and the

DMAi forward-direction address pointer is incremented.

(3) If the DMA transfer counter underflows, the DMA enable bit changes to “0” and the DMA transfer

is completed. The DMA interrupt request bit changes to “1” simultaneously.

Figure 2.103: Operation of one-shot transfer mode

Item

Set-up

Transfer space

O From any SFR, ROM or RAM address to a fixed address

From a fixed address to any ROM, RAM or SFR address

From one fixed address to another fixed address

Unit of transfer

O 8 bits

16 bits

Dummy

cycle

Source

Source

Dummy

cycle

Dummy

cycle

internal clock Φ

Address bus

Data bus

DMAi

request bit

DMA transfer

counter

DMAi

interrupt

request bit

DMAi

enable bit

Write signal to

software DMAi

request bit

CPU use Source

Source

Dummy

cycle

Indeterminate 0016

• In the case in which the number of transfer times is set to 2.

(1) Request signal for a DMA transfer occurs

Cleared to “0” when interrupt request is

accepted, or cleared by software

(2) Data transfer begins

CPU use

CPU use

FF16

(3) Underflow

CPU useCPU use

CPU use

Destination Destination

Destination

Destination

0116

Loading...

Loading...