Frequency Synthesizer

M30240 Group

Rev.1.00 Sep 24, 2003 Page 292 of 360

3.1.4.5 Frequency Divider

Clock f

SYN is a divided down version of fVCO. fsyn is generated via the Frequency Synthesizer Divide

register (FSD). When the Frequency Synthesizer Divider register is set to 255, division is disabled and

f

SYN = fVCO. Table 3.4 shows some examples of how the frequency synthesizer division register is set.

f

SYN = fVCO / 2(m+1) m: FSD value

Note 1: Set f

SYN to 12MHz or lower.

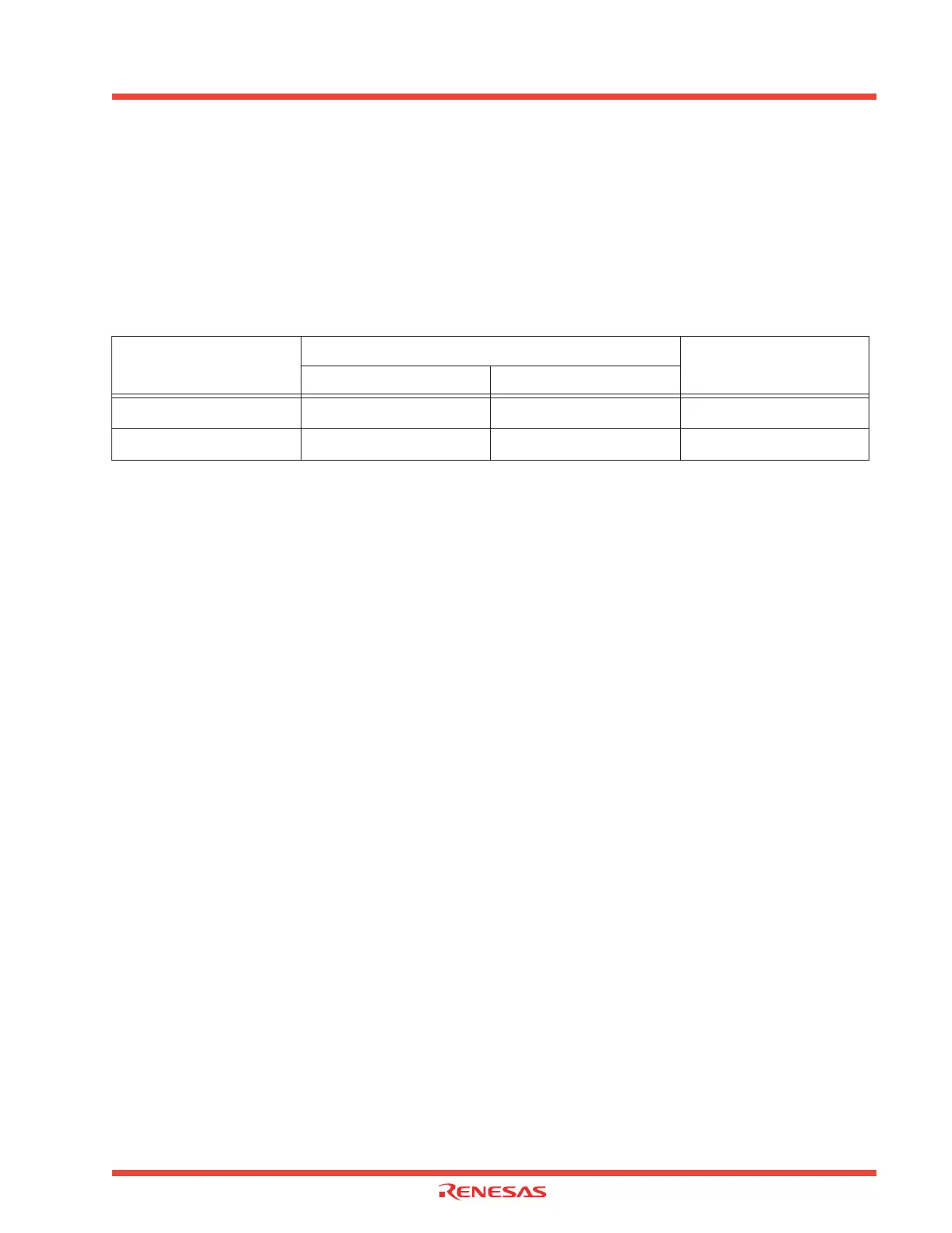

Table 3.4: Example of Setting the Frequency Synthesizer Divide Register (FSD)

fVCO

FSD

fSYN

Decimal List Hexadecimal List

48.00 MHz

1

01

16

12.00 MHz

48.00 MHz

127

7F

16

187.50 MHz

Loading...

Loading...