Universal Serial Bus

M30240 Group

Rev.1.00 Sep 24, 2003 Page 319 of 360

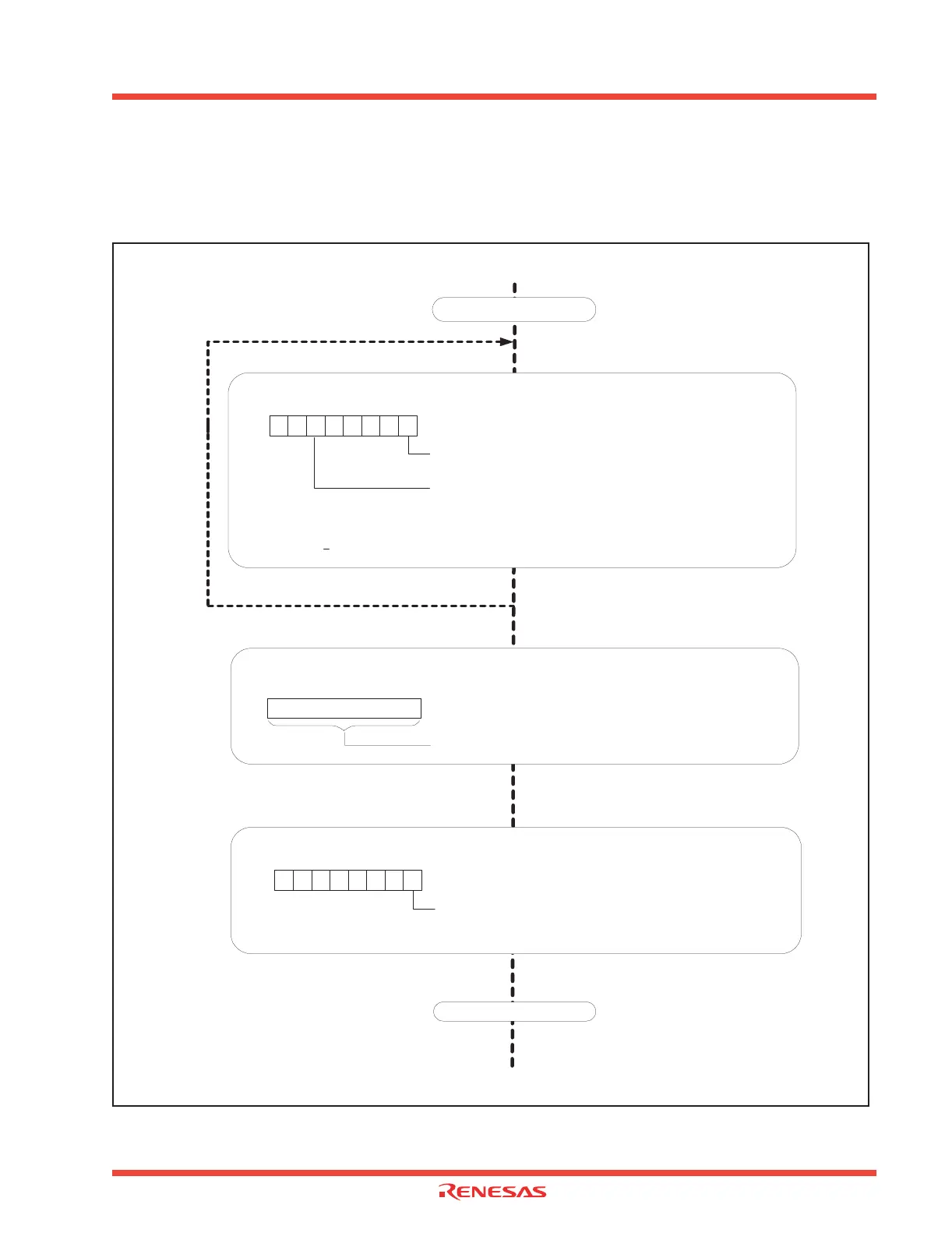

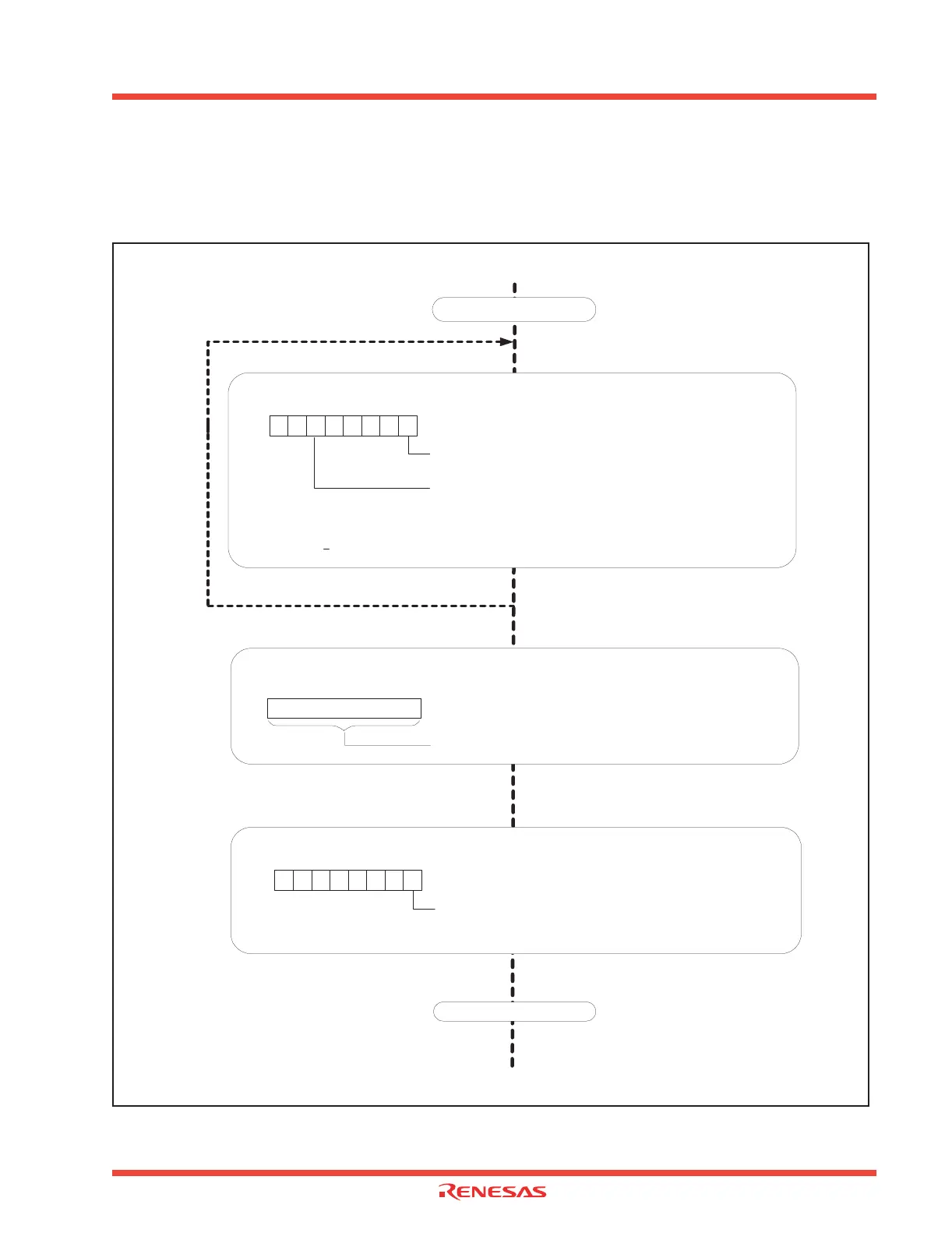

3.2.10 USB Transmission (IN)

Figure 3.32 shows the procedures for Endpoints 1-4 USB IN transmission. Use caution when using

isochronous transfer and the UNDER_RUN is “1” because a USB Endpoint x IN interrupt will occur.

Figure 3.32: Procedures for sending USB Transmission

USB Endpoint x FIFO Address

EPi (i = 1-4) 0339

16, 033A16,

033B16, 033C16

Transmission Data

b7

b0

Setting Transmission Data IN FIFO

USB Endpoint x IN Interrupt Processing Routine

Confirm Data Transmission in FIFO

USB Endpoint x IN Control and Status Register Address

EPiICS (i = 1-4) 0319

16, 032116,

032916, 033116

IN_PKT_RDY Bit

0 : Not ready

1 : Ready

TX_NOT_EPT Bit (Note)

o : Transmit FIFO is empty

1 : Transmit FIFO is not empty

b7 b0

Register Evacuation Process

Note: In the case of double buffer mode, 1 data packet remains in FIFO when the IN_PKT_RDY is "0" and the TX_NOT_EPT

is "1" (packet size < half FIFO size.) When the remaining data is transmitted with the next IN token, the TX_NOT_EPT is

automatically cleared.

Setting IN_PKT_RDY

USB Endpoint x IN Control and Status Register Address

EPiICS (i = 1-4) 0319

16, 032116,

032916, 033116

IN_PKT_RDY Bit (Note)

1 : Data Packet Ready

b7 b0

Note: If the transmission data is a short packet or if the AUTO-SET bit is "0" the user must set to "1".

1

Register Recover Processing

Execute REIT Command

0

0

Loading...

Loading...