Clock-Asynchronous Serial I/O

M30240 Group

Rev.1.00 Sep 24, 2003 Page 209 of 360

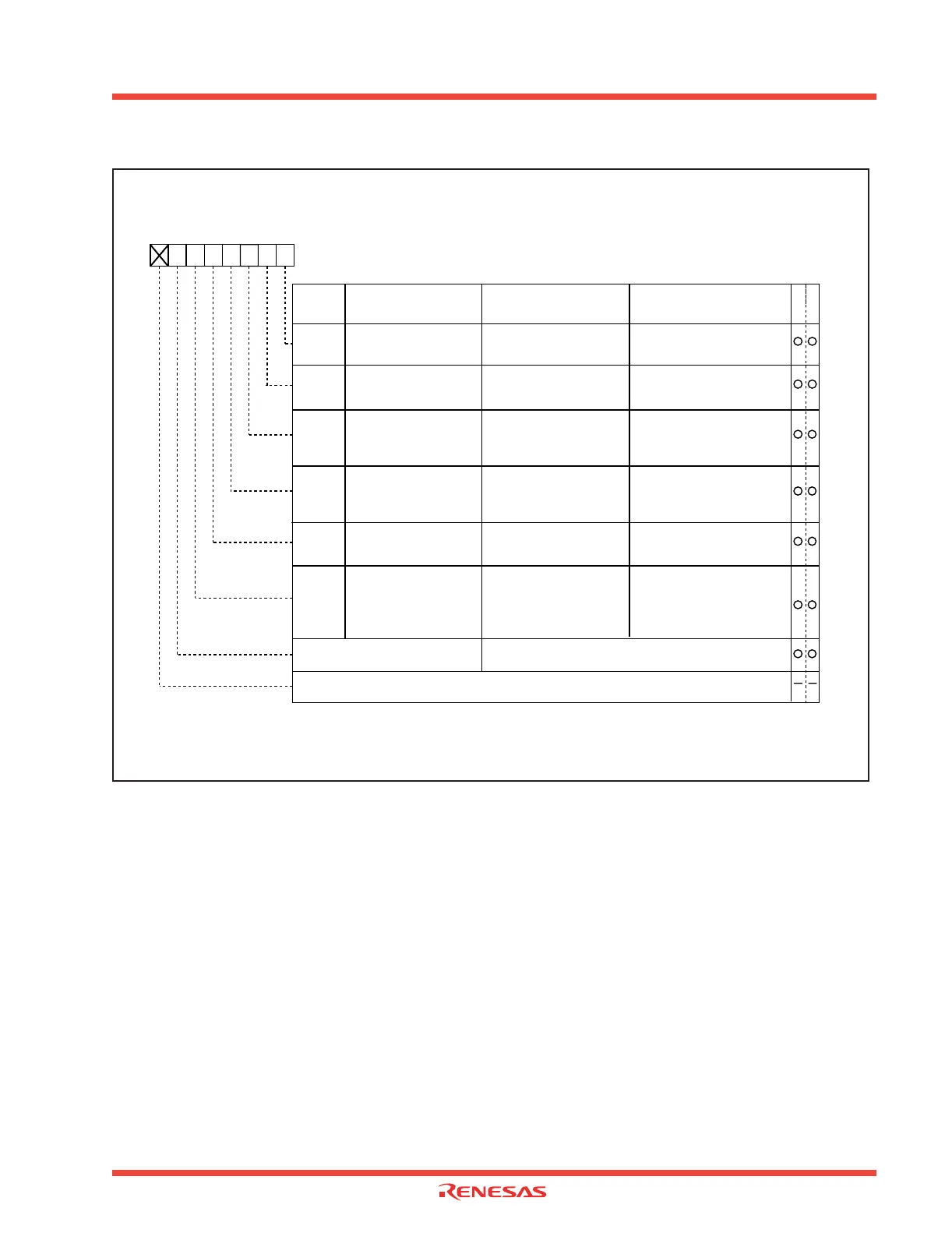

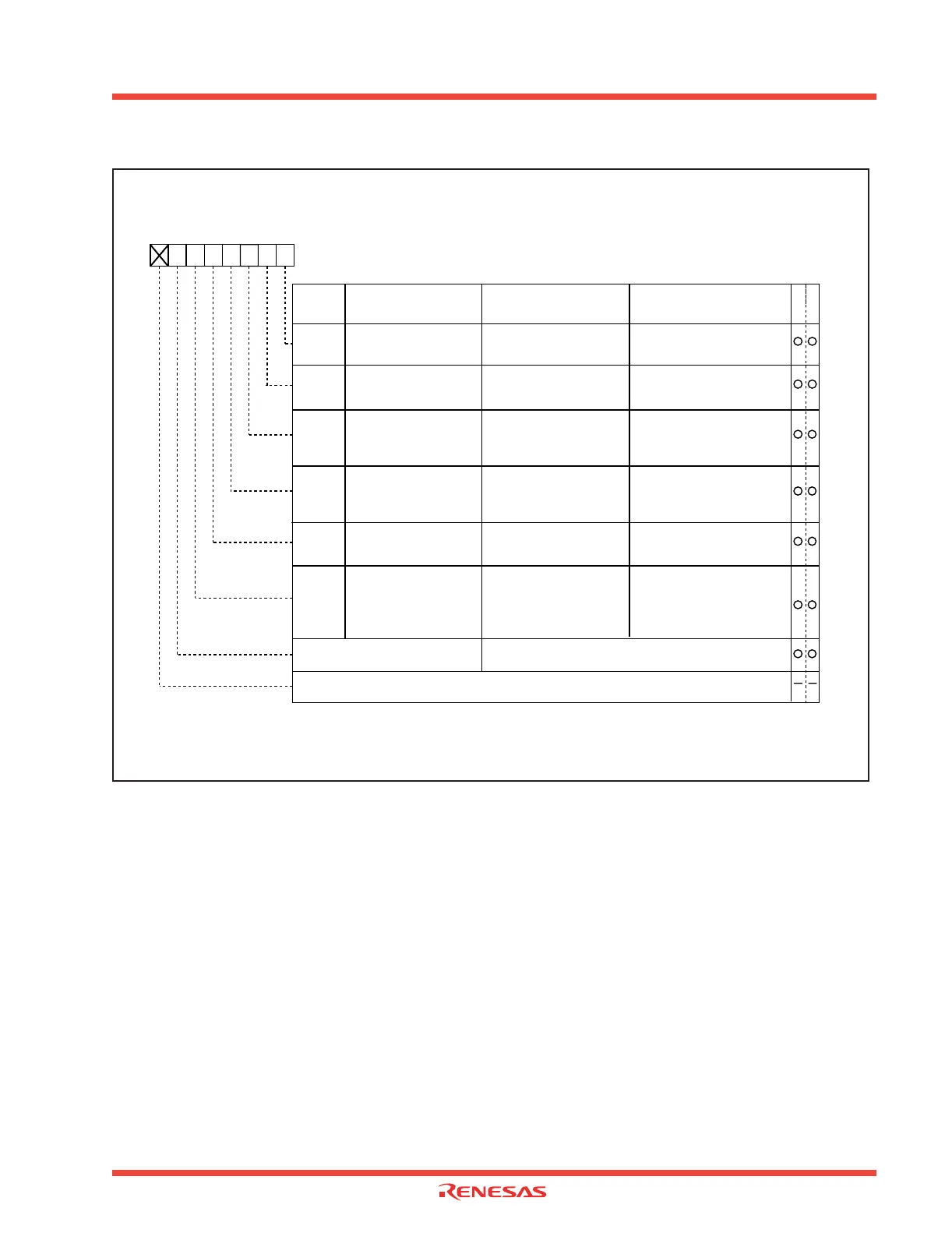

Figure 2.61: UARTi related registers (5)

Note: When using multiple pins to output the transfer clock, the following requirements must be met:

• UART1 internal/external clock select bit (bit 3 at address 03A8

16) = “0”.

UART transmit/receive control register 2

Symbol Address When reset

UCON 03B0

16 X00000002

b7 b6 b5 b4 b3 b2 b1 b0

Bit name

Bit

symbol

WR

Function

(During UART mode)

Function

(During clock synchronous

serial I/O mode)

CLKMD0

CLKMD1

UART0 transmit

interrupt cause select bit

UART0 continuous

receive mode enable bit

0 : Continuous receive

mode disabled

1 : Continuous receive

mode enable

UART1 continuous

receive mode enable bit

CLK/CLKS select bit 0

UART1 transmit

interrupt cause select bit

0 : Transmit buffer empty (Tl = 1)

1 : Transmission completed

(TXEPT = 1)

0 : Transmit buffer empty (Tl = 1)

1 : Transmission completed

(TXEPT = 1)

0 : Normal mode

(CLK output is CLK1 only)

1 : Transfer clock output

from multiple pins

function selected

0 : Continuous receive

mode disabled

1 : Continuous receive

mode enabled

Nothing is assigned.

0 : Transmit buffer empty (Tl = 1)

1 : Transmission completed

(TXEPT = 1)

0 : Transmit buffer empty (Tl = 1)

1 : Transmission completed

(TXEPT = 1)

Must always be “0”

U0IRS

U1IRS

U0RRM

U1RRM

Invalid

Invalid

Invalid

CLK/CLKS select

bit 1 (Note)

Valid when bit 5 = “1”

0 : Clock output to CLK1

1 : Clock output to CLKS1

Must always be “0”

Reserved

Write "0" when writing to this bit. The value is "0" when read.

0

Loading...

Loading...