Clock-Asynchronous Serial I/O

M30240 Group

Rev.1.00 Sep 24, 2003 Page 211 of 360

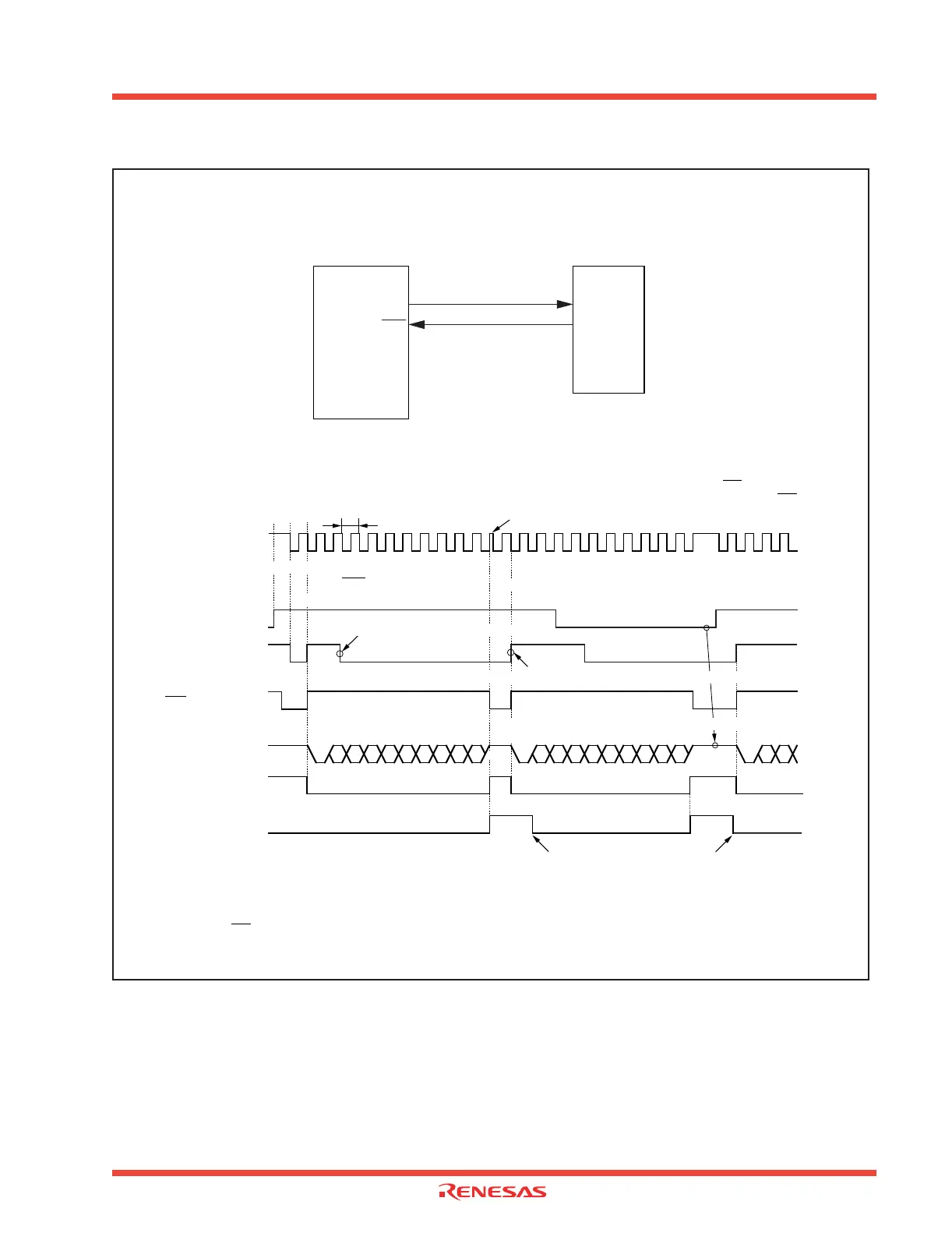

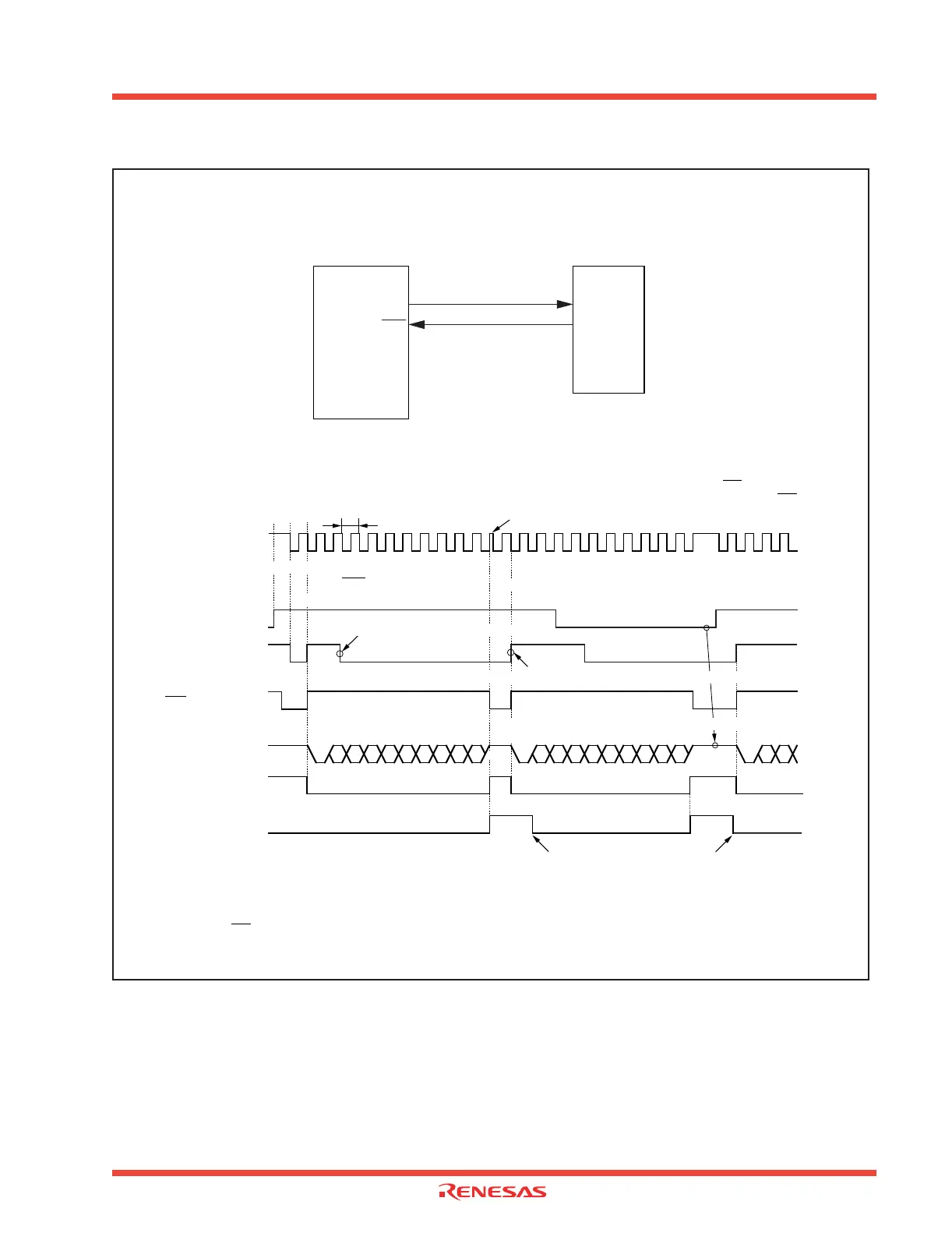

Figure 2.62: Operation timing of transmission in UART mode

Example of wiring

Example of operation

T

X

Di

CTSi

R

X

D

Port

Microcomputer Receiver side IC

Transmit

enable bit (TE)

Transmit buffer

empty flag (Tl)

Transmit

register empty

flag (TXEPT)

D0 D1 D2

D3

D4

D5 D6

D7ST

P

Start

bit

Parity

bit

TxDi

CTSi

“0”

“1”

“0”

“1”

“L”

“H”

“0”

“1”

Transmit

interrupt request

bit (IR)

“0”

“1”

Cleared to “0” when interrupt request is accepted, or cleared by software

D0 D1 D2

D3

D4

D5 D6

D7ST

P

SP

D

0 D1

ST

Shown in ( ) are bit symbols.

SP

Stopped pulsing because transfer enable bit = “0”

Stop

bit

Data is set in UARTi transmit buffer register

Transferred from UARTi transmit buffer register to UARTi transmit register

Tc

Transfer clock

(1) Transmission enabled

(2) Confirm

CTS

(3) Start transmission

(4) Confirm stop bit

(5) Start transmission

The above timing applies to the following settings :

• Parity is enabled.

• One stop bit.

• CTS function is selected.

• Transmit interrupt cause select bit = “1”.

Tc = 16 (n + 1) / fi or 16 (n + 1) / fEXT

fi : frequency of BRGi count source (f1, f8, f32)

f

EXT : frequency of BRGi count source (external clock)

n : value set to BRGi

When confirming stop bit, transfer clock is stopped momentarily because CTS = "H".

The transfer clock is started again to begin transmitting immediately after confirming CTS = "L".

• Transmit data length is 8 bits.

Loading...

Loading...