UART0 to UART2

M30240 Group

Rev.1.00 Sep 24, 2003 Page 79 of 360

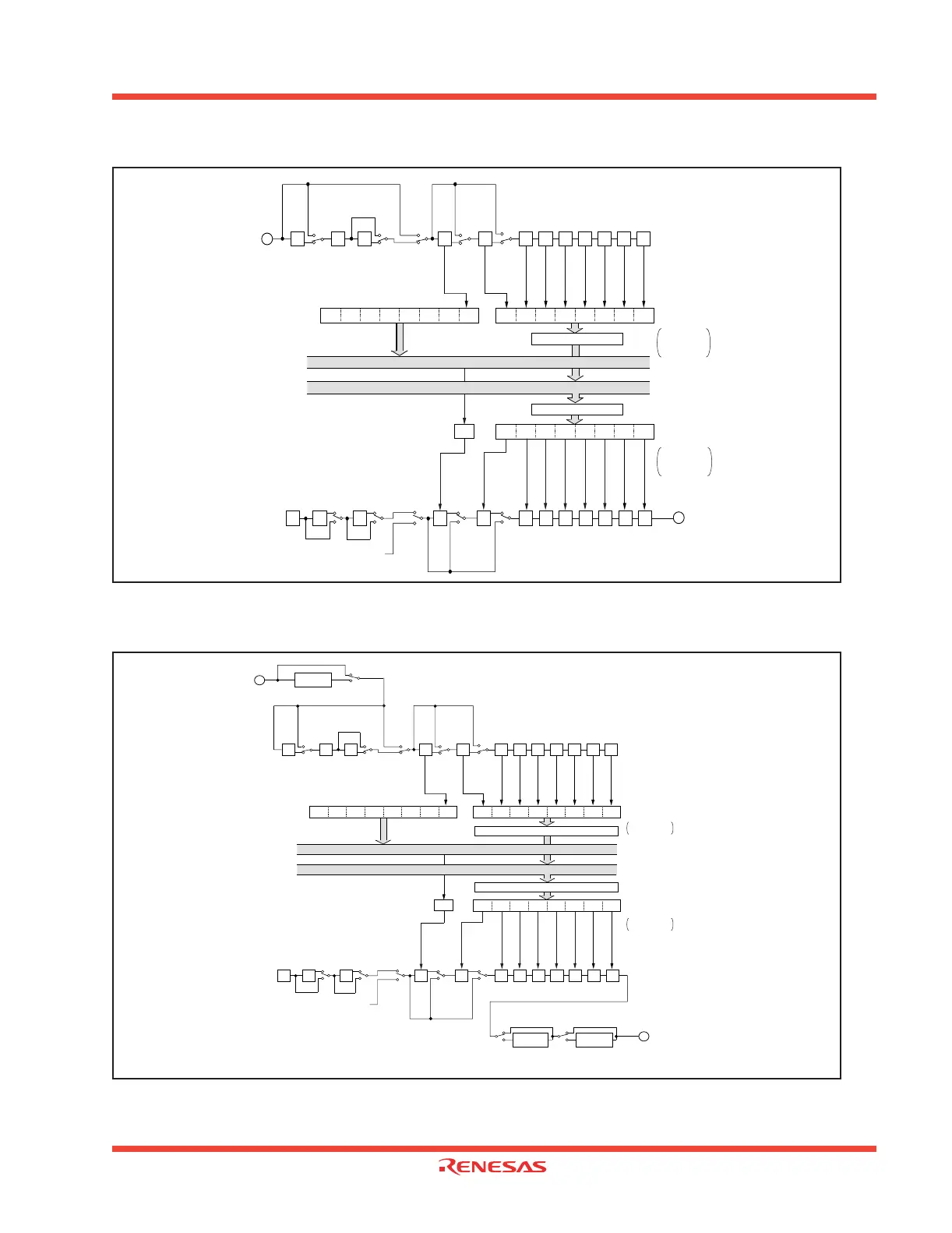

Figure 1.74: Block diagram of UARTi (i=0,1) transmit/receive circuit

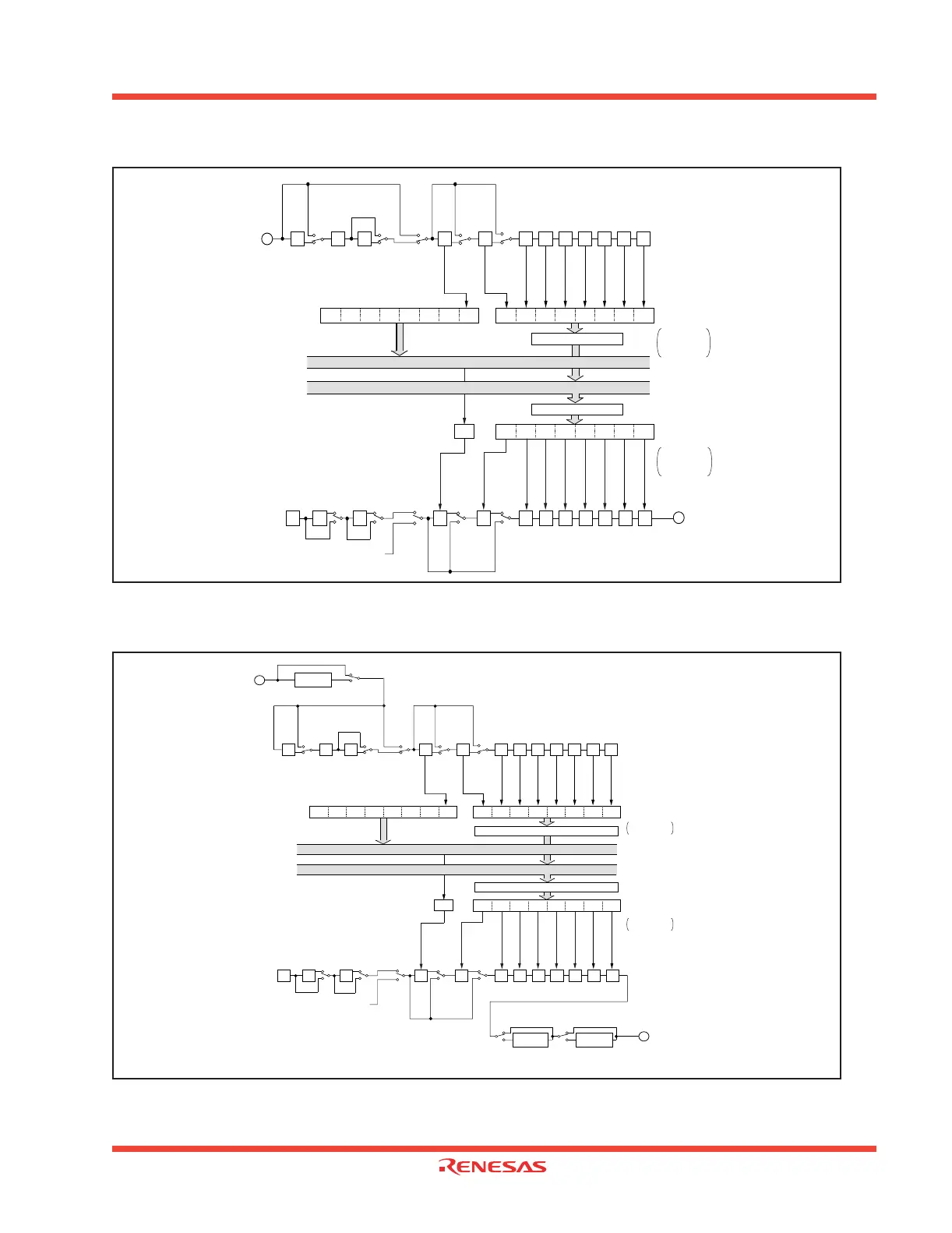

Figure 1.75: Block diagram of UART2 transmit/receive circuit

SP SP

PA R

2SP

1SP

UART

UART (7 bits)

UART (8 bits)

UART (7 bits)

UART (9 bits)

Clock

synchronous

type

Clock synchronous

type

TxDi

UARTi transmit register

PAR

enabled

PAR

disabled

D8

D7 D6 D5 D4 D3 D2 D1 D0

SP: Stop bit

PAR: Parity bit

UARTi transmit

buffer register

MSB/LSB conversion circuit

UART (8 bits)

UART (9 bits)

Clock synchronous

type

UARTi receive

buffer register

UARTi receive register

2SP

1SP

PAR

enabled

PAR

disabled

UART

UART (7 bits)

UART (9 bits)

Clock

synchronous

type

Clock

synchronous type

UART (7 bits)

UART (8 bits)

RxDi

Clock

synchronous type

UART (8 bits)

UART (9 bits)

Address 03A6

16

Address 03A7

16

Address 03AE

16

Address 03AF

16

Address 03A2

16

Address 03A3

16

Address 03AA

16

Address 03AB

16

Data bus low-order bits

MSB/LSB conversion circuit

D7 D6 D5 D4 D3 D2 D1 D0D8

0000000

SP SP

PA R

“0”

2SP

1SP

UART

UART

(7 bits)

UART

(8 bits)

UART(7 bits)

UART

(9 bits)

Clock

synchronous

type

Clock

synchronous type

Data bus low-order bits

TxD2

UART2 transmit register

PAR

disabled

PAR

enabled

D8

D7 D6 D5 D4 D3 D2 D1 D0

UART2 transmit

buffer register

UART

(8 bits)

UART

(9 bits)

Clock

synchronous type

UART2 receive

buffer register

UART2 receive register

2SP

1SP

UART

(7 bits)

UART

(8 bits)

UART(7 bits)

UART

(9 bits)

Clock

synchronous type

Clock

synchronous type

RxD2

UART

(8 bits)

UART

(9 bits)

Address 037E

16

Address 037F16

Address 037A16

Address 037B16

Data bus high-order bits

D7 D6 D5 D4 D3 D2 D1 D0D8

0000000

SP SP

PA R

“0”

Reverse

No reverse

Error signal

output circuit

RxD data

reverse circuit

Error signal output

enable

Error signal output

disable

Reverse

No reverse

Logic reverse circuit + MSB/LSB conversion circuit

Logic reverse circuit + MSB/LSB conversion circuit

PAR

enabled

PAR

disabled

UART

Clock

synchronous

type

TxD data

reverse circuit

SP: Stop bit

PAR: Parity bit

PAR: Parity bit

Loading...

Loading...