RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1419

Dec 10, 2015

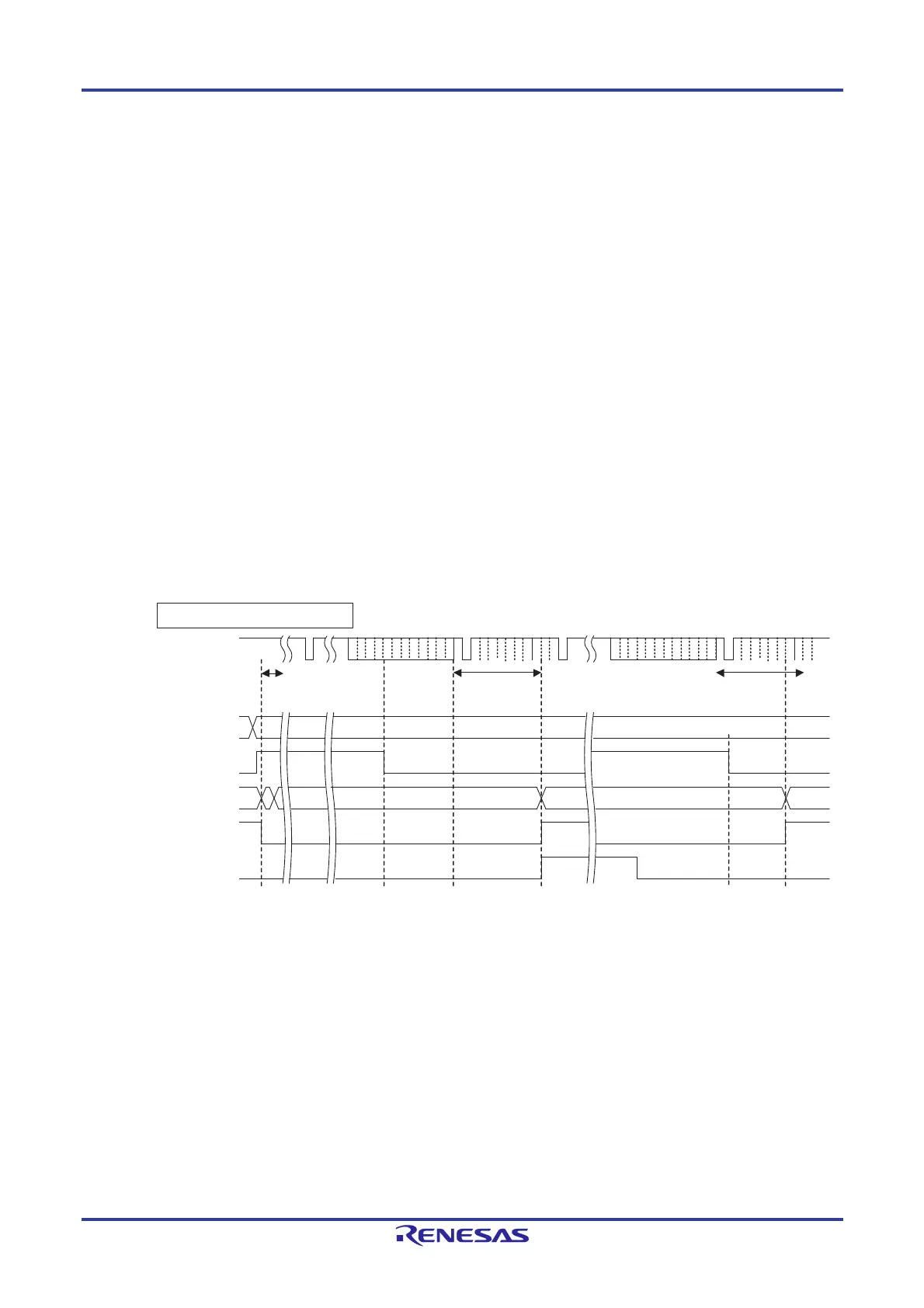

(1) While the CAN bus is idle, when the CFE value in the CFCCLk register is 1 (transmit/receive FIFO buffer k is used)

and the CFDC[2:0] value in the CFCCLk register is B'001 (4 messages) or more and the CFMC[5:0] value in the

CFSTSk register is H'01 or more, the priority determination processing starts to determine the highest-priority

transmit message. When the highest-priority transmit message has been determined, transmission of the message

starts.

(2) When a transmit request from a buffer is present, the priority determination starts with the CRC delimiter for the next

transmission.

(3) When transmit completes successfully, the CFMC[5:0] value in the CFSTSk register is decremented. Setting the

CFIM bit in the CFCCLk register to 1 (a FIFO transmit interrupt request is generated each time a message has been

transmitted) sets the CFTXIF flag in the CFSTSk register to 1 (a transmit/receive FIFO transmit interrupt request is

present).

(4) The CFTXIF flag can be cleared by the program.

(5) Message transmission from transmit/receive FIFO buffer k has been completed and the CFMC[5:0] value in the

CFSTSk register is decremented. The CFMC[5:0] bits are cleared to H'00 and therefore the CFEMP flag in the

CFSTSk register is set to 1 (the transmit/receive FIFO buffer contains no message (buffer empty)).

Transmission is continued until the CFEMP flag is set to 1. It is possible to continuously store transmit messages in

FIFO buffers until the CFFLL flag in the CFSTSk register is set to 1 (the transmit/receive FIFO buffer is full).

Figure 18-31. Transmit/Receive FIFO Buffer Transmission Timing Chart

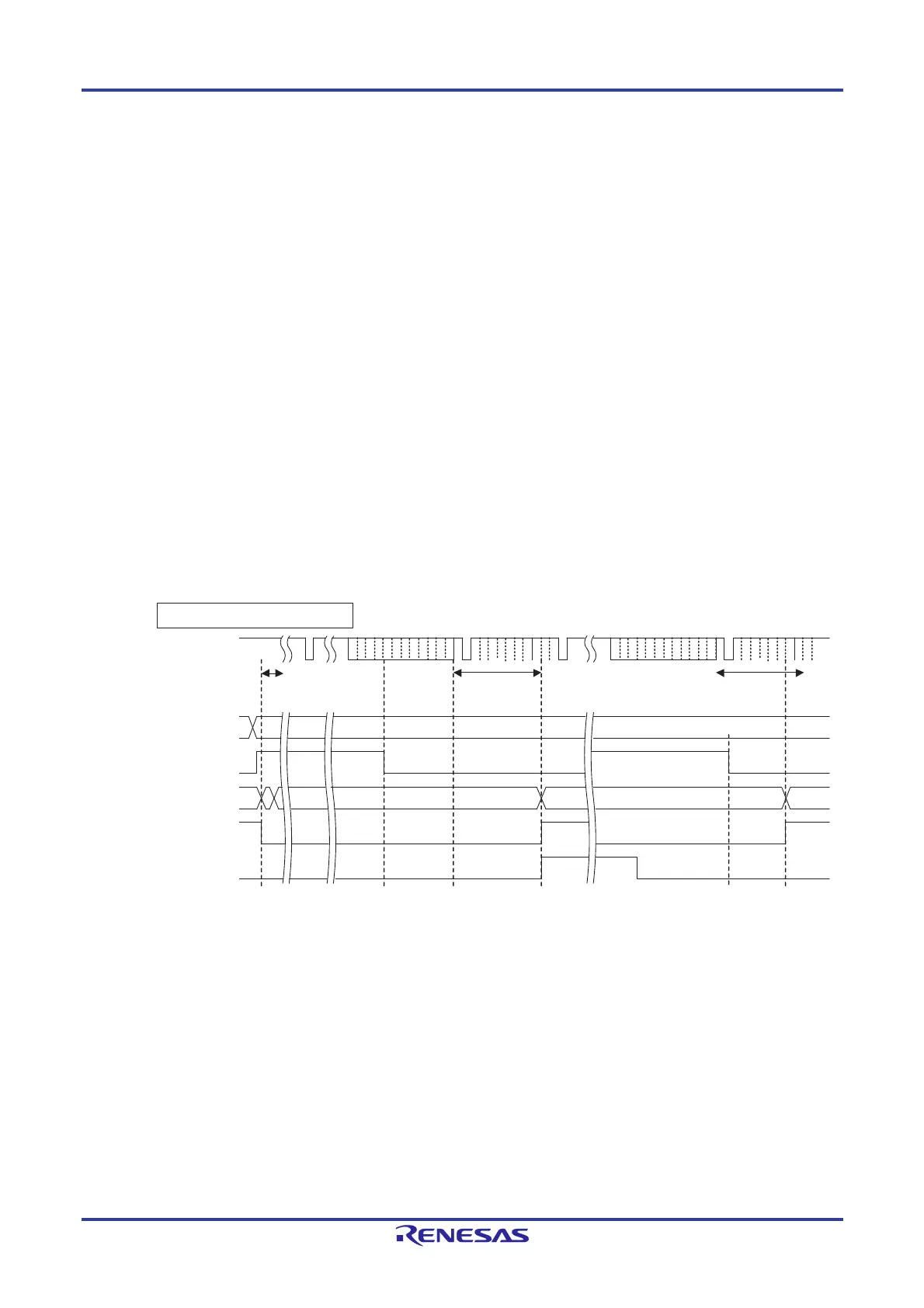

(Transmit Abort Completed)

(1) While the CAN bus is idle, when the CFE value in the CFCCLk register is 1 (transmit/receive FIFO buffer k is used)

and the CFDC[2:0] value in the CFCCLk register is B'001 (4 messages) or more and the CFMC[5:0] value in the

CFSTSk register is H'01 or more, the priority determination processing starts to determine the highest-priority

transmit message. When the highest-priority transmit message has been determined, transmission of the message

starts.

(2) When transmission is in progress or it is determined that the transmit/receive FIFO buffer is used for the next

transmission, message transmission is not aborted unless an error or arbitration lost occurs even if the CFE bit is

set to 0 (no transmit/receive FIFO buffer k is used).

(3) When a transmit request from a buffer is present, the priority determination starts with the CRC delimiter for the next

transmission. In this figure, transmit/receive FIFO buffer k is not selected as a buffer for the next transmission.

(1) (3) (4)

SOF

EOF

INT

SOF

EOF

INT

(6)

0 1

(5)

3

2

0

0

1

0

(2)

H

L

1

0

1

0

1

0

CFDC[2:0], CFE: Bits in the CFCCLk register

CFMC[5:0], CFEMP, CFTXIF: Flags in the CFSTSk register

CAN bus

CFDC[2:0] bits

CFE bit

CFMC[5:0] bits

CFEMP flag

CFTXIF flag

[Transmit/receive FIFO buffer k]

CRC

delimiter

CRC

delimiter

Determine next

transmit priority

Determine next

transmit priority

Determine next

transmit priority

Remark k = 0

Example of transmission from transmit/receive

FIFO buffer k

Loading...

Loading...