RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 115

Dec 10, 2015

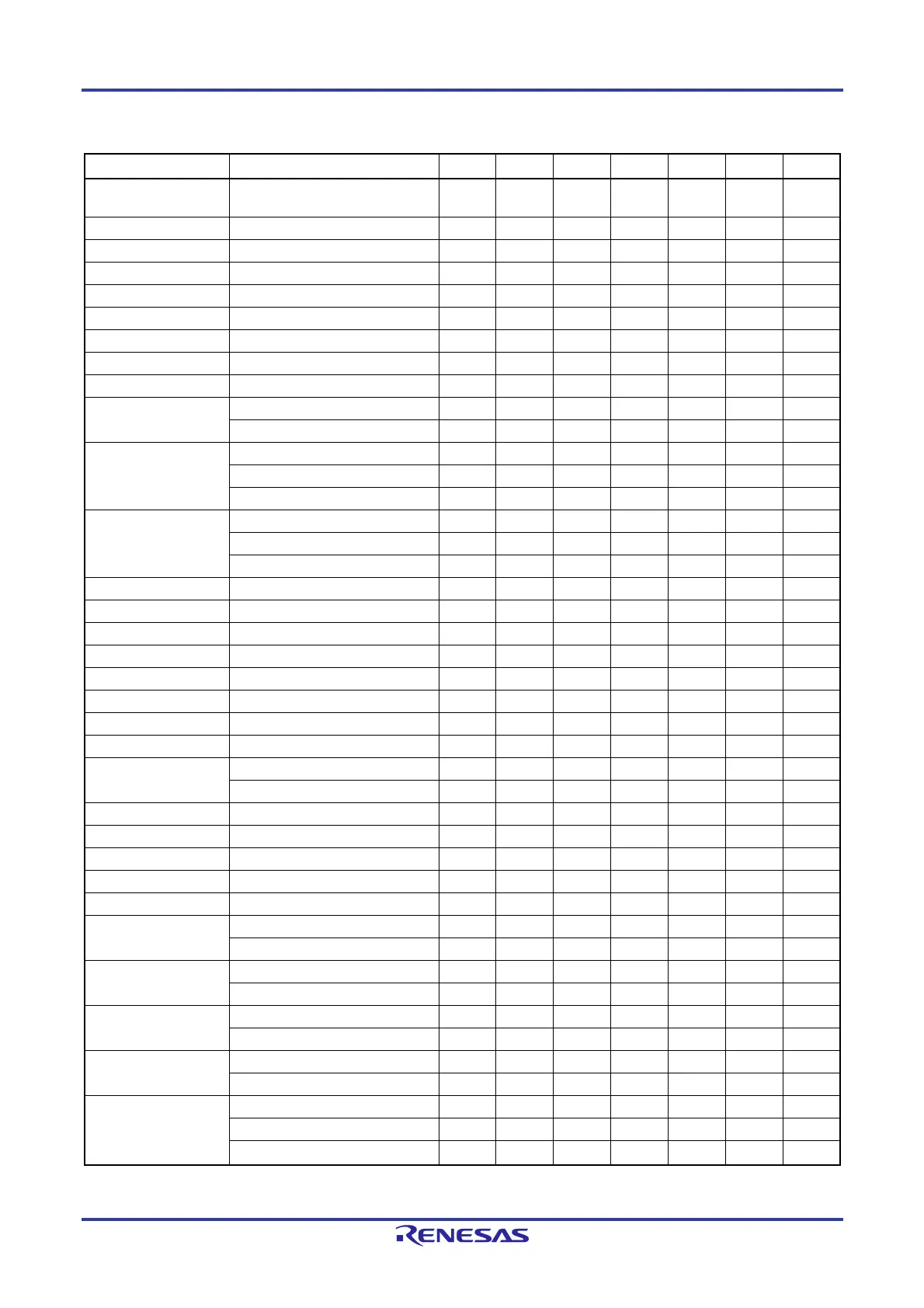

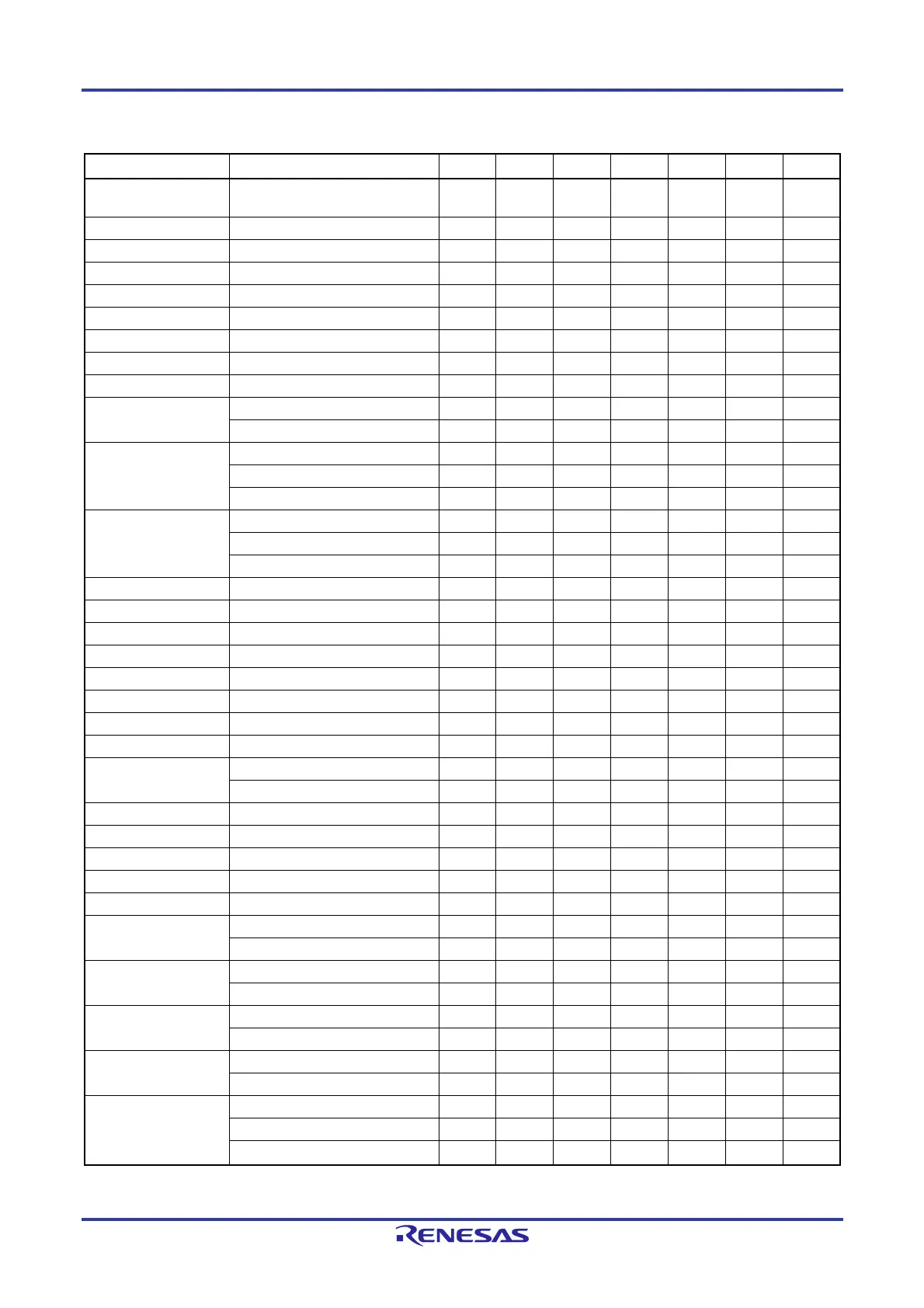

Table 3-3. Vector Table (1/2)

Vector Table Address Interrupt Source 100-pin 80-pin 64-pin 48-pin 32-pin 30-pin 20-pin

0000H

RESET, POR, LVD, WDT,

TRAP, IAW, CLM

0004H INTWDTI

0006H INTLVI

0008H INTP0

000AH INTP1

000CH INTP2

000EH INTP3

0010H INTP4/INTSPM

0012H INTP5/INTCMP0

0014H INTP13

INTCLM

0016H INTST0

INTCSI00

INTIIC00

0018H INTSR0

INTCSI01

INTIIC01

001AH INTTRD0

001CH INTTRD1

001EH INTTRJ0

0020H INTRAM

0022H INTLIN0TRM

0024H INTLIN0RVC

0026H INTLIN0STA/INTLIN0

0028H INTIICA0

002AH INTP8

INTRTC

002CH INTTM00

002EH INTTM01

0030H INTTM02

0032H INTTM03

0034H INTAD

0036H INTP6

INTTM11H

0038H INTP7

INTTM13H

003AH INTP9

INTTM01H

003CH INTP10

INTTM03H

003EH INTST1

INTCSI10

INTIIC10

Loading...

Loading...