RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 116

Dec 10, 2015

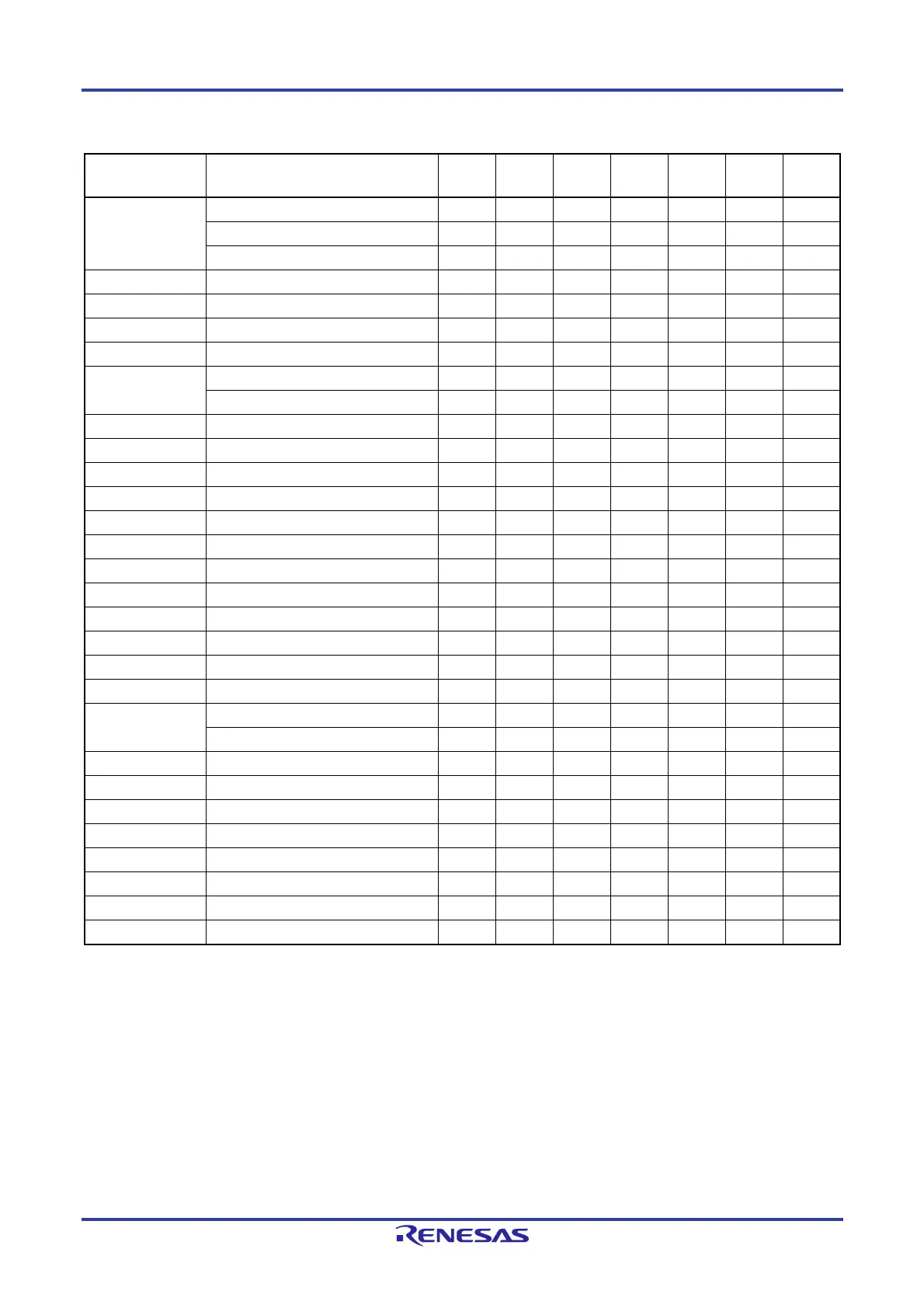

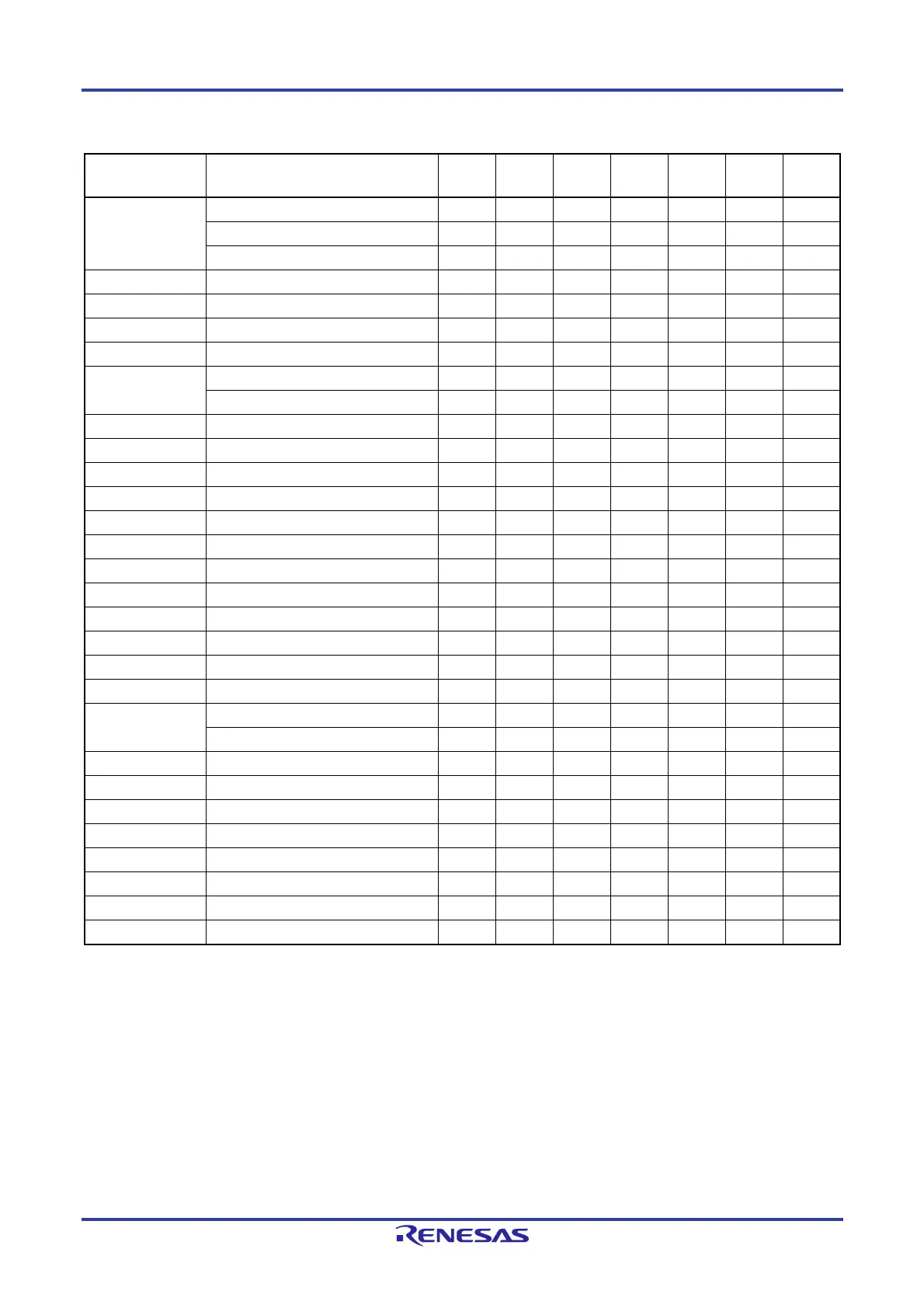

Table 3-3. Vector Table (2/2)

Vector Table

Address

Interrupt Source 100-pin 80-pin 64-pin 48-pin 32-pin 30-pin 20-pin

0040H INTSR1

–

INTCSI11

– – –

INTIIC11

– – –

0042H INTTM04

0044H INTTM05

0046H INTTM06

0048H INTTM07

004AH INTP11

– – – –

INTLIN0WUP

004CH INTKR

004EH INTCAN0ERR

–

0050H INTCAN0WUP

–

0052H INTCAN0CFR

–

0054H INTCAN0TRM

–

0056H INTCANGRFR

–

0058H INTCANGERR

–

005AH INTTM10

–

005CH INTTM11

–

005EH INTTM12

–

0060H INTTM13

–

0062H INTFL

0064H INTP12

– – – –

INTLIN1WUP

– – –

0066H INTLIN1TRM

– – –

0068H INTLIN1RVC

– – –

006AH INTLIN1STA/INTLIN1

– – –

006CH INTTM14

– – –

006EH INTTM15

– – –

0070H INTTM16

– – –

0072H INTTM17

– – –

007EH BRK

(2) CALLT instruction table area

The 64-byte area 00080H to 000BFH can store the subroutine entry address of a 2-byte call instruction (CALLT). Set

the subroutine entry address to a value in a range of 00000H to 0FFFFH (because an address code is 2 bytes).

To use the boot swap function, set a CALLT instruction table also at 02080H to 020BFH.

(3) Option byte area

A 4-byte area of 000C0H to 000C3H can be used as an option byte area. Set the option byte at 020C0H to 020C3H

when the boot swap is used. For details, see CHAPTER 29 OPTION BYTE.

Loading...

Loading...