RL78/F13, F14 CHAPTER 6 TIMER ARRAY UNIT

R01UH0368EJ0210 Rev.2.10 477

Dec 10, 2015

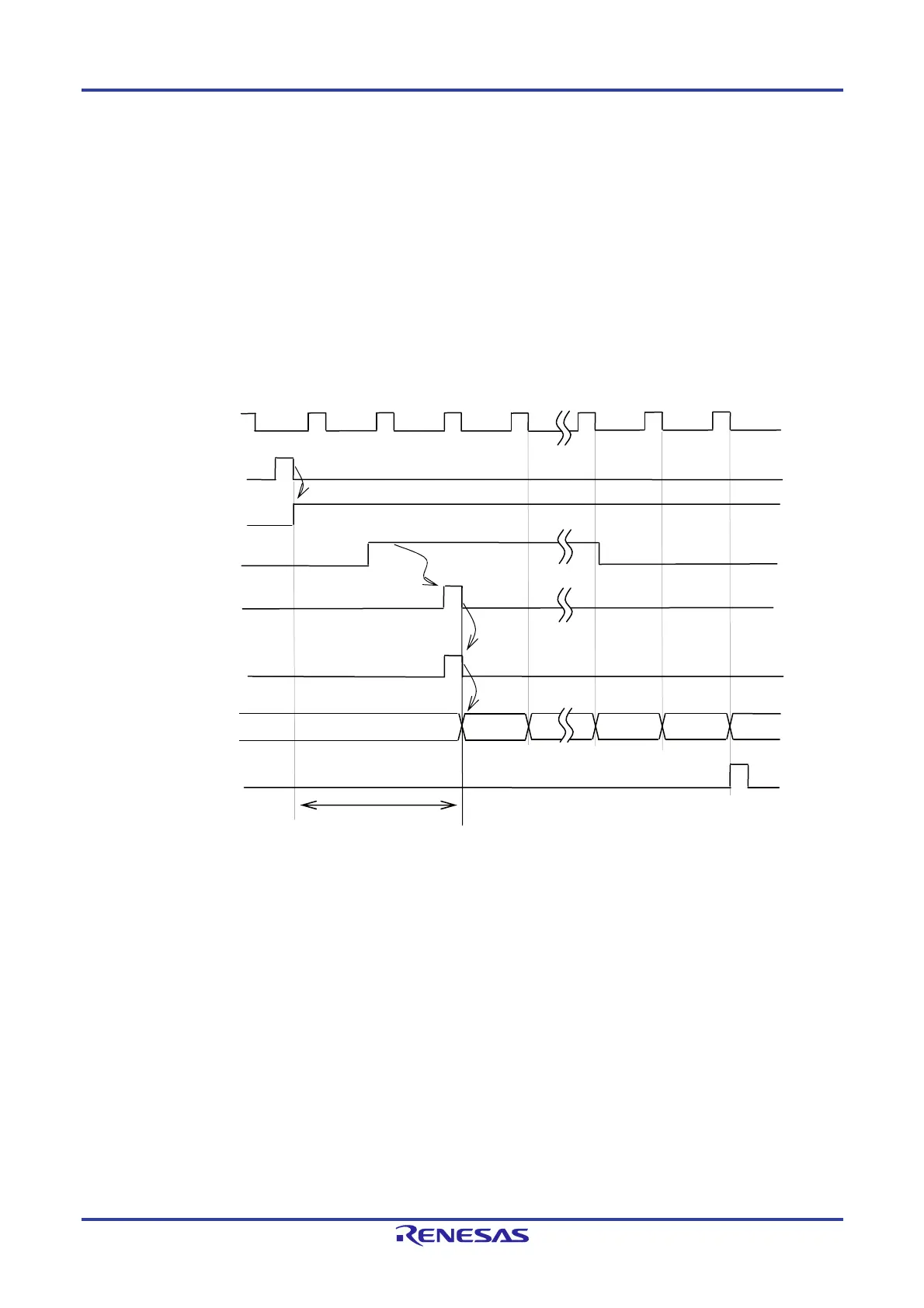

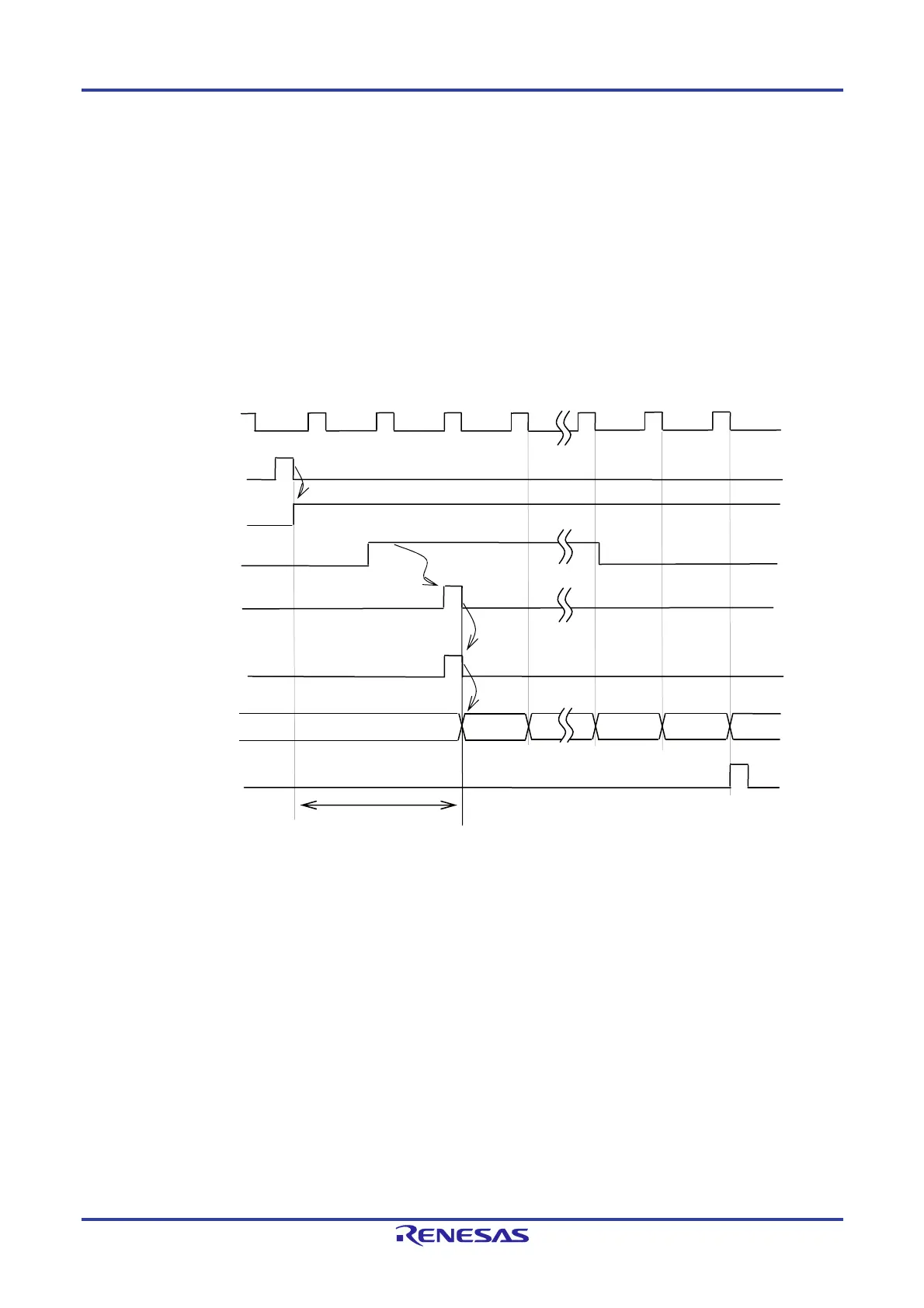

(4) Start timing in one-count mode

<1> Operation is enabled (TEmn = 1) by writing 1 to the TSmn bit.

<2> Timer count register mn (TCRmn) holds the initial value until start trigger generation.

<3> Rising edge of the TImn input is detected.

<4> On start trigger detection, the value of timer data register mn (TDRmn) is loaded to the TCRmn register and

count starts.

<5> When the TCRmn register counts down and its count value is 0000H, INTTMmn is generated and the value of

the TCRmn register becomes FFFFH and counting stops

.

Figure 6-32. Start Timing (In One-count Mode)

Remark The timing is shown in Figure 6-32 indicates while the noise filter is not used. By making the noise filter

on-state, the edge detection becomes 2 f

MCK cycles (it sums up to 3 to 4 cycles) later than the normal cycle

of TImn input. The error per one period occurs be the asynchronous between the period of the TImn input

and that of the count clock (f

MCK).

f

MC

(f

TCLK

)

TSmn(Write)

TEmn

TImn input

<1>

<2>

Rising edge

Edge detection

<4>

TCRmn

Initial value

1

Start trigger

detection signal

<3>

m

0

FFFF

INTTMmn

Start trigger input wait status

<5>

Loading...

Loading...