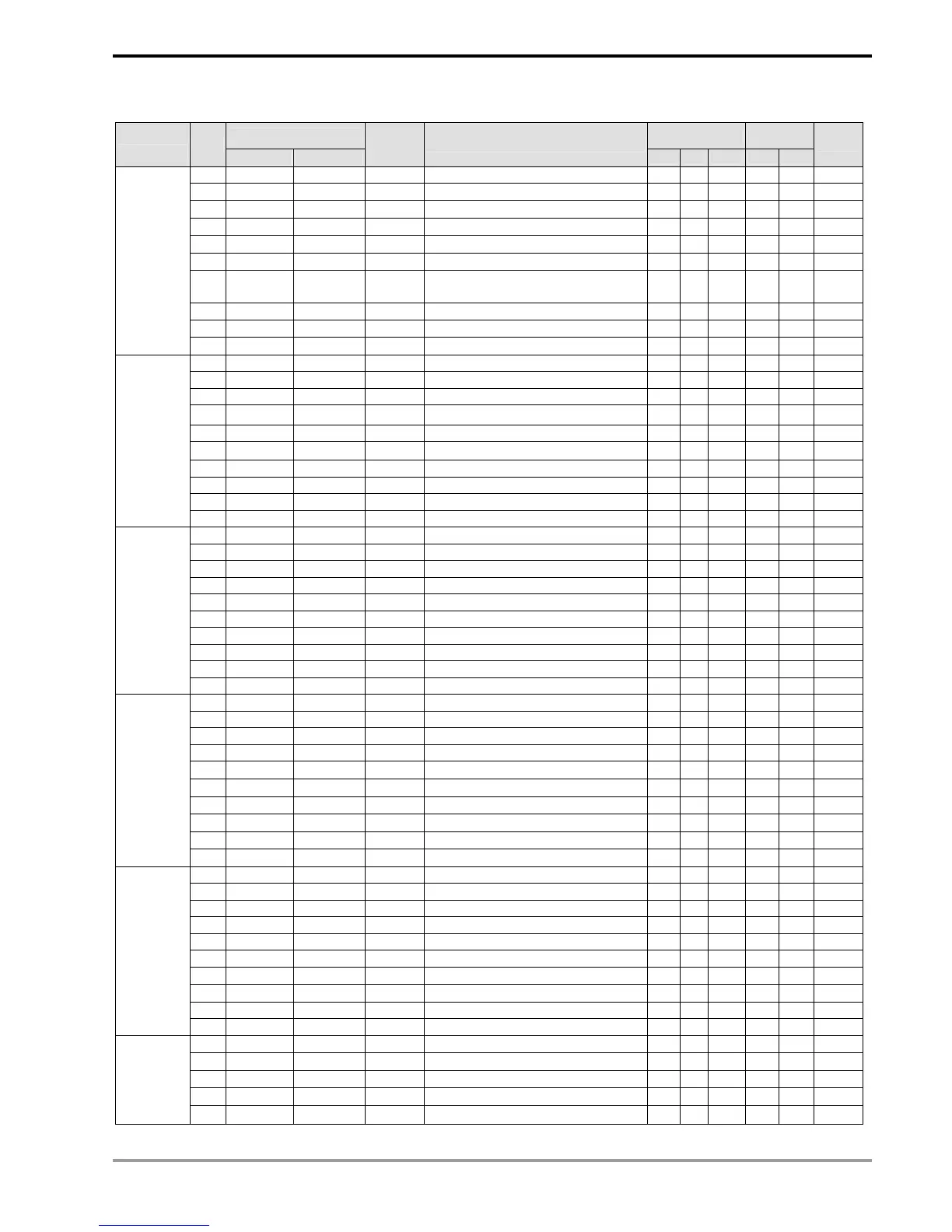

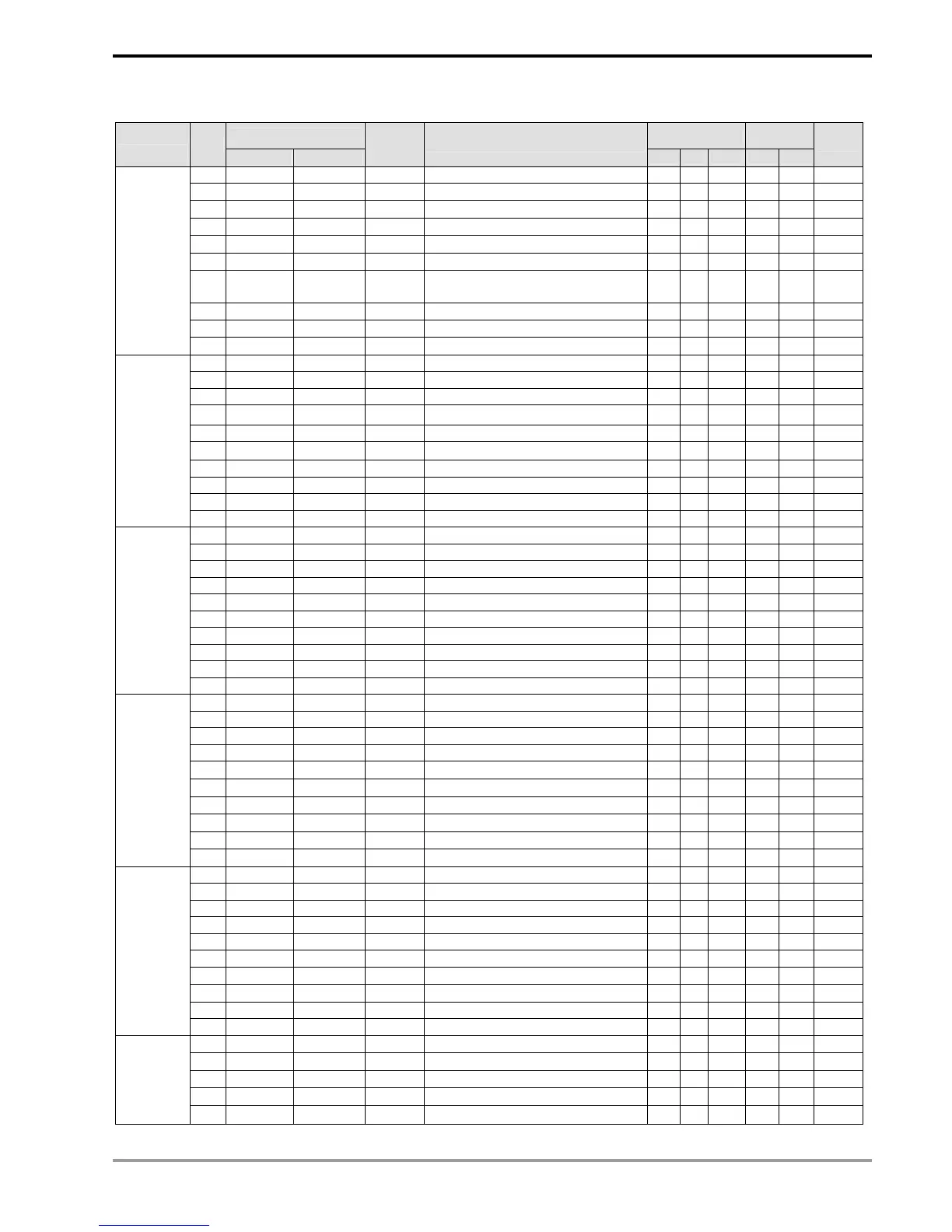

5 Categories & Use of Application Instructions

DVP-PLC Application Manual

5-1

5.1 List of Instructions

Mnemonic

Applicable to STEPS

Category

API

16-bit 32-bit

P

instruction

Function

ES SA EH 16-bit 32-bit

Page

00

CJ -

3

Conditional Jump

3 3 3

3 - 6-1

01

CALL -

3

Call Subroutine

3 3 3

3 - 6-5

02

SRET -

-

Subroutine Return

3 3 3

1 - 6-5

03

IRET -

-

Interrupt Return

3 3 3

1 - 6-8

04

EI -

-

Enable Interrupts

3 3 3

1 - 6-8

05

DI -

-

Disable Interrupts

3 3 3

1 - 6-8

06

FEND -

-

The End of The Main Program

(First End)

3 3 3

1 - 6-12

07

WDT -

3

Watchdog Timer Refresh

3 3 3

1 - 6-14

08

FOR -

-

Start of a FOR-NEXT loop

3 3 3

3 - 6-15

Loop Control

09

NEXT -

-

End of a FOR-NEXT loop

3 3 3

1 - 6-15

10

CMP DCMP

3

Compare

3 3 3

7136-18

11

ZCP DZCP

3

Zone Compare

3 3 3

9176-19

12

MOV DMOV

3

Move

3 3 3

5 9 6-20

13

SMOV -

3

Shift Move

–

3 3

11 - 6-21

14

CML DCML

3

Compliment

3 3 3

5 9 6-23

15

BMOV -

3

Block Move

3 3 3

7

–

6-24

16

FMOV DFMOV

3

Fill Move

3 3 3

7136-26

17

XCH DXCH

3

Exchange

3 3 3

5 9 6-27

18

BCD DBCD

3

Binary Coded Decimal

3 3 3

5 9 6-29

Transmission

Comparison

19

BIN DBIN

3

Binary

3 3 3

5 9 6-30

20

ADD DADD

3

Addition

3 3 3

7136-32

21

SUB DSUB

3

Subtraction

3 3 3

7136-34

22

MUL DMUL

3

Multiplication

3 3 3

7136-35

23

DIV DDIV

3

Division

3 3 3

7136-37

24

INC DINC

3

Increment

3 3 3

3 5 6-39

25

DEC DDEC

3

Decrement

3 3 3

3 5 6-40

26

WAND DAND

3

Logical Word AND

3 3 3

7136-41

27

WOR DOR

3

Logical Word OR

3 3 3

7136-42

28

WXOR DXOR

3

Logical Exclusive OR

3 3 3

7136-43

Four Arithmetic

Operation

29

NEG DNEG

3

2’s Complement (Negative)

3 3 3

3 5 6-44

30

ROR DROR

3

Rotation Right

3 3 3

5 9 6-46

31

ROL DROL

3

Rotation Left

3 3 3

5 9 6-47

32

RCR DRCR

3

Rotation Right with Carry

3 3 3

5 9 6-48

33

RCL DRCL

3

Rotation Left with Carry

3 3 3

5 9 6-49

34

SFTR

-

3

Bit Shift Right

3 3 3

9

-

6-50

35

SFTL

-

3

Bit Shift Left

3 3 3

9

-

6-51

36

WSFR

-

3

Word Shift Right

-

3 3

9

-

6-52

37

WSFL

-

3

Word Shift Left

-

3 3

9

-

6-54

38

SFWR

-

3

Shift Register Write

-

3 3

7

-

6-55

Rotation &

Displacement

39

SFRD -

3

Shift Register Read

-

3 3

7 - 6-56

40

ZRST -

3

Zero Reset

3 3 3

5 - 6-57

41

DECO -

3

Decode

3 3 3

7 - 6-59

42

ENCO -

3

Encode

3 3 3

7 - 6-61

43

SUM DSUM

3

Sum of Active Bits

3 3 3

5 9 6-63

44

BON DBON

3

Check Specified Bit Status

3 3 3

7136-64

45

MEAN DMEAN

3

Mean

3 3 3

7136-65

46

ANS -

-

Timed Annunciator Set

-

3 3

7 - 6-66

47

ANR -

3

Annunciator Reset

-

3 3

1 - 6-66

48

SQR DSQR

3

Square Root

3 3 3

5 9 6-72

Data Processing

49

FLT DFLT

3

Floating Point

3 3 3

5 9 6-70

50

REF -

3

Refresh

3 3 3

5 - 7-1

51

REFF -

3

Refresh and Filter Adjust

-

3 3

3 - 7-2

52

MTR -

-

Input Matrix

-

3 3

9 - 7-3

53

- DHSCS

-

High Speed Counter Set

3 3 3

- 13 7-5

High Speed

Processing

54

- DHSCR

-

High Speed Counter Reset

3 3 3

–

13 7-15

Loading...

Loading...