9 Application Instructions API 150-199

DVP-PLC Application Manual

9-64

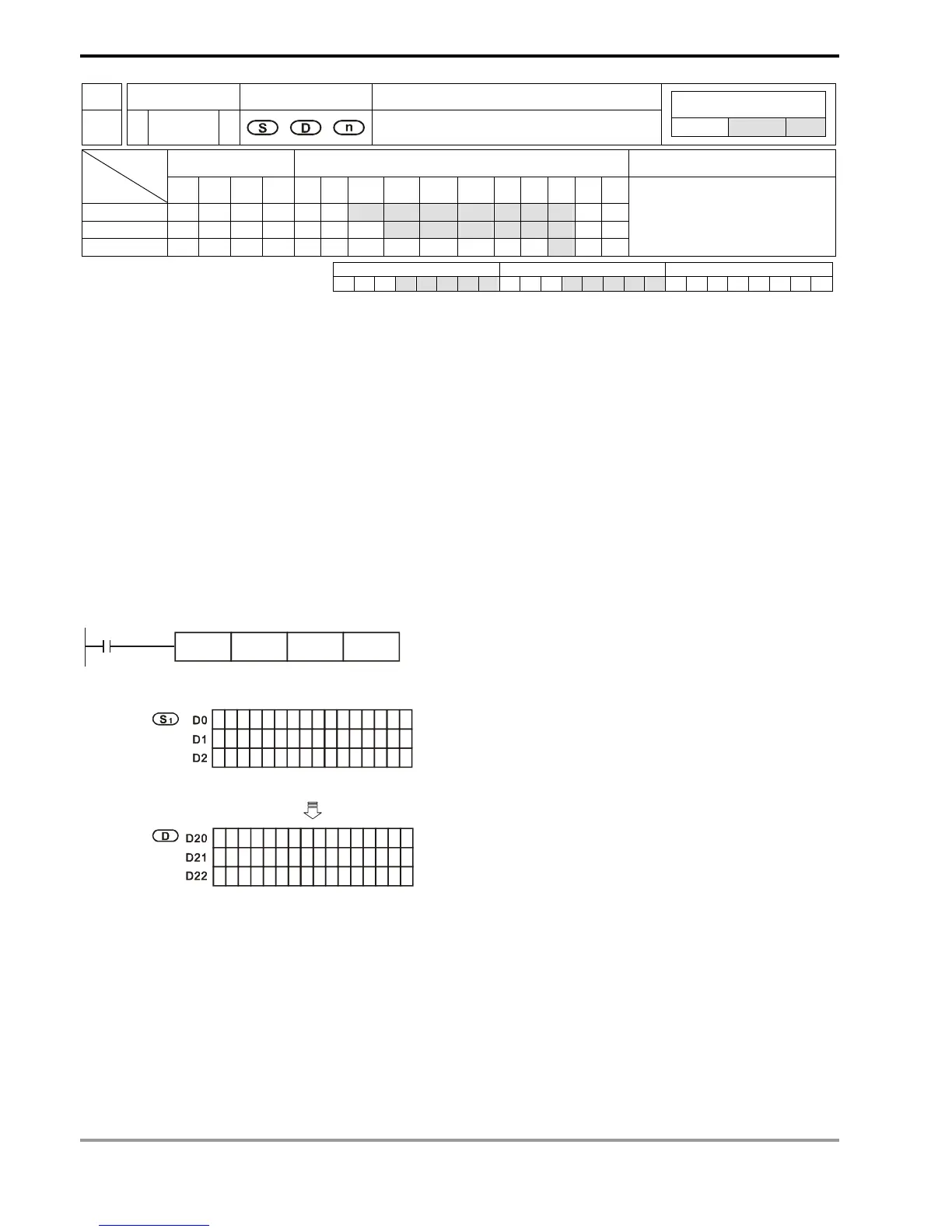

API Mnemonic Operands Function

184

MINV P

Matrix Inverse Operation

Controllers

ES/EX/SS SA/SX/SC EH/SV

Bit Devices Word Devices Program Steps Type

OP

X Y M S K H KnX KnY KnM KnS T C D E F

S * * * * * * *

D * * * * * *

n * * *

MINV, MINVP: 7 steps

PULSE 16-bit 32-bit

ES EX SS SA SX SC EH SV ES EX SS SA SX SC EH SV ES EX SS SA SX SC EH SV

Operands:

S: Matrix source device D: Operation result n: Array length

Explanations:

1. Range of n: K1 ~ K256

2. S designates KnX, KnY, KnM and KnS; D designates KnY, KnM and KnS.

3. SA/SX/SC can designate n = 4. EH/EH2/SV can designate n 4≦ .

4. See the specifications of each model for their range of use.

5. S performs an inverse matrix operation according to the array length n. The result is stored in D.

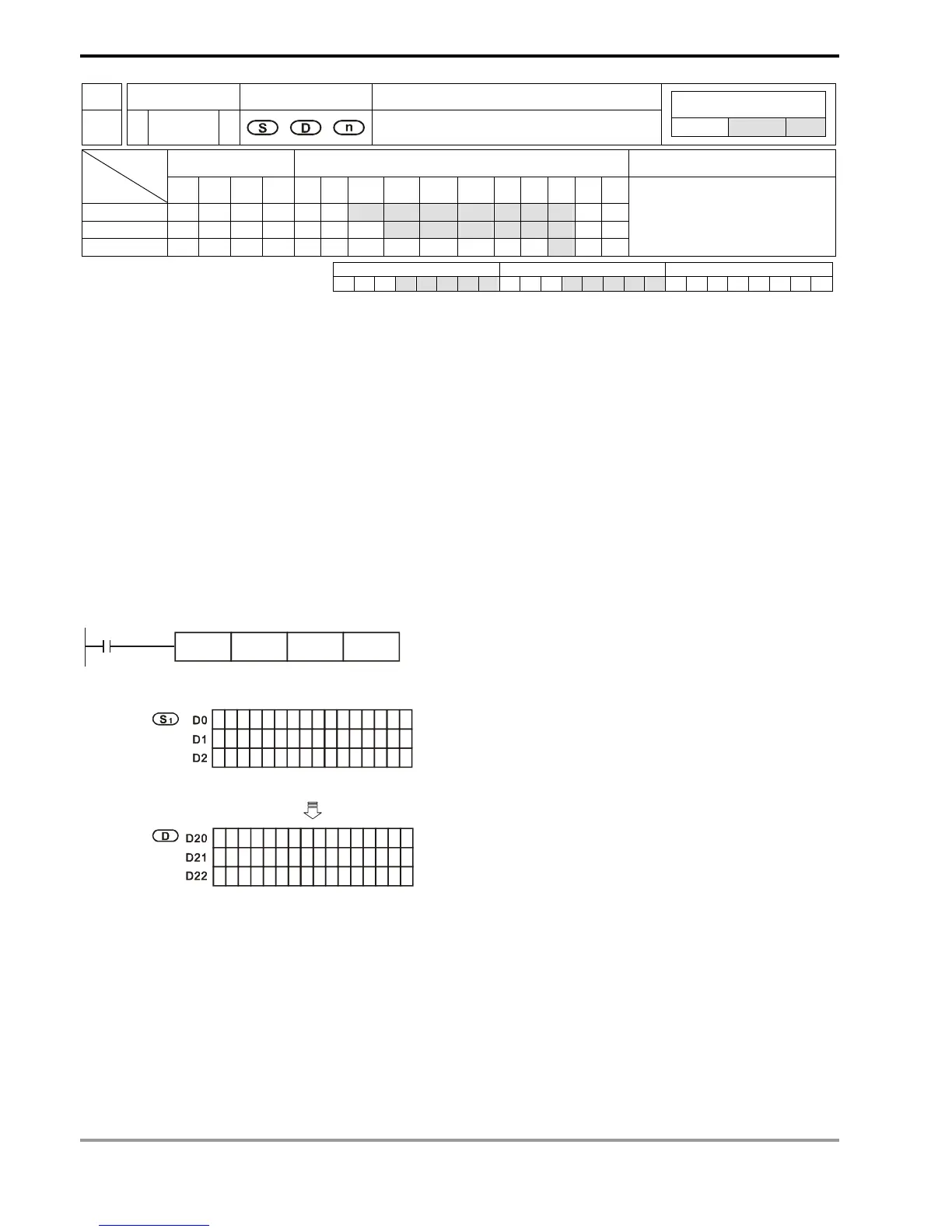

Program Example:

When X0 = On, the 3 arrays of 16-bit registers D0 ~ D2 perform a matrix inverse operation. The result will be stored in

the 3 arrays of 16-bit registers D20 ~ D22.

X0

MINV D0 D20 K3

Before

Execution

After

Execution

0

0

0

11

1

1

1

1

0

0

0

0

0

0

11

1

1

1

1

0

0

0

1

1

1

0

0

0

1

1

1

0

0

0

1

1

1

0

0

0

1

1

1

0

0

0

1010101010101010

1010101010101010

1010101010101010

b15 b0

MINV

Loading...

Loading...