159

CHAPTER 3 FUNCTIONS

3

3.11 Monitor Function

3.11.4 Executional conditioned device test

3.11.4 Executional conditioned device test

This function changes a device value within the specified step of a program.Note 3.5

This enables debugging of the specified ladder block without modifying the program.

*1

*1 The executional conditioned device test is not available for the SFC program.

(1) Operation of the executional conditioned device test

A device value will be changed based on the registration data once after the executional conditioned device test

setting is registered.

The changed device value becomes enabled in the ladder blocks of the specified step number and later.

Note that a device value is changed within the specified step regardless of an execution status of the instruction in

the specified step.

Note 3.5

Before executing the function with the Q02UCPU, Q03UDCPU, Q04UDHCPU, Q06UDHCPU, Q13UDHCPU, or

Q26UDHCPU, check the versions of the CPU module and programming tool used.

( Page 465, Appendix 2)

Universal

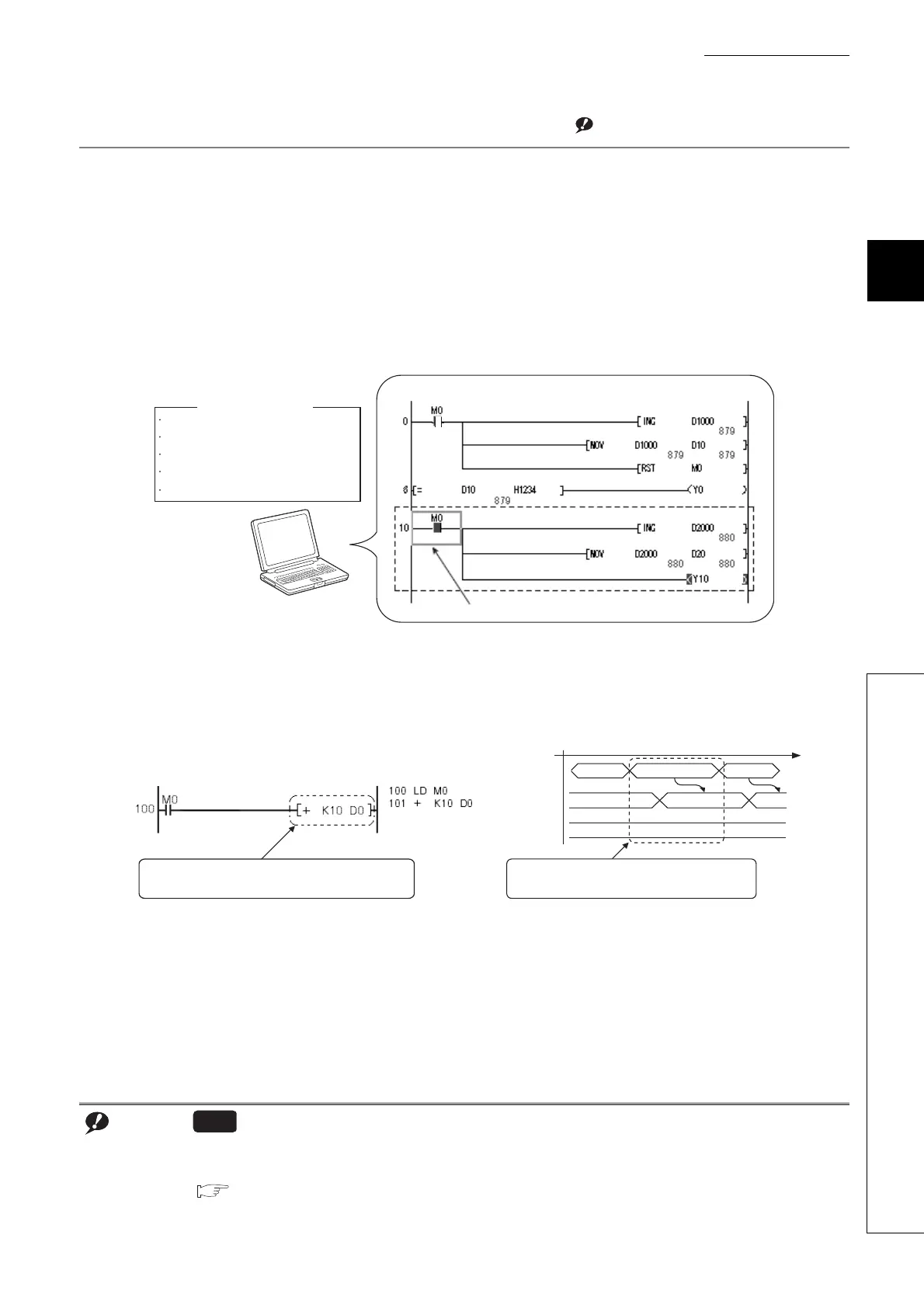

Programming tool

Program name

Step No.

Device

Setting value

Execution timing

: MAIN

: 10

: M0

: ON

: Before executing instruction

Registration data

M0 is turned on.

Program: MAIN

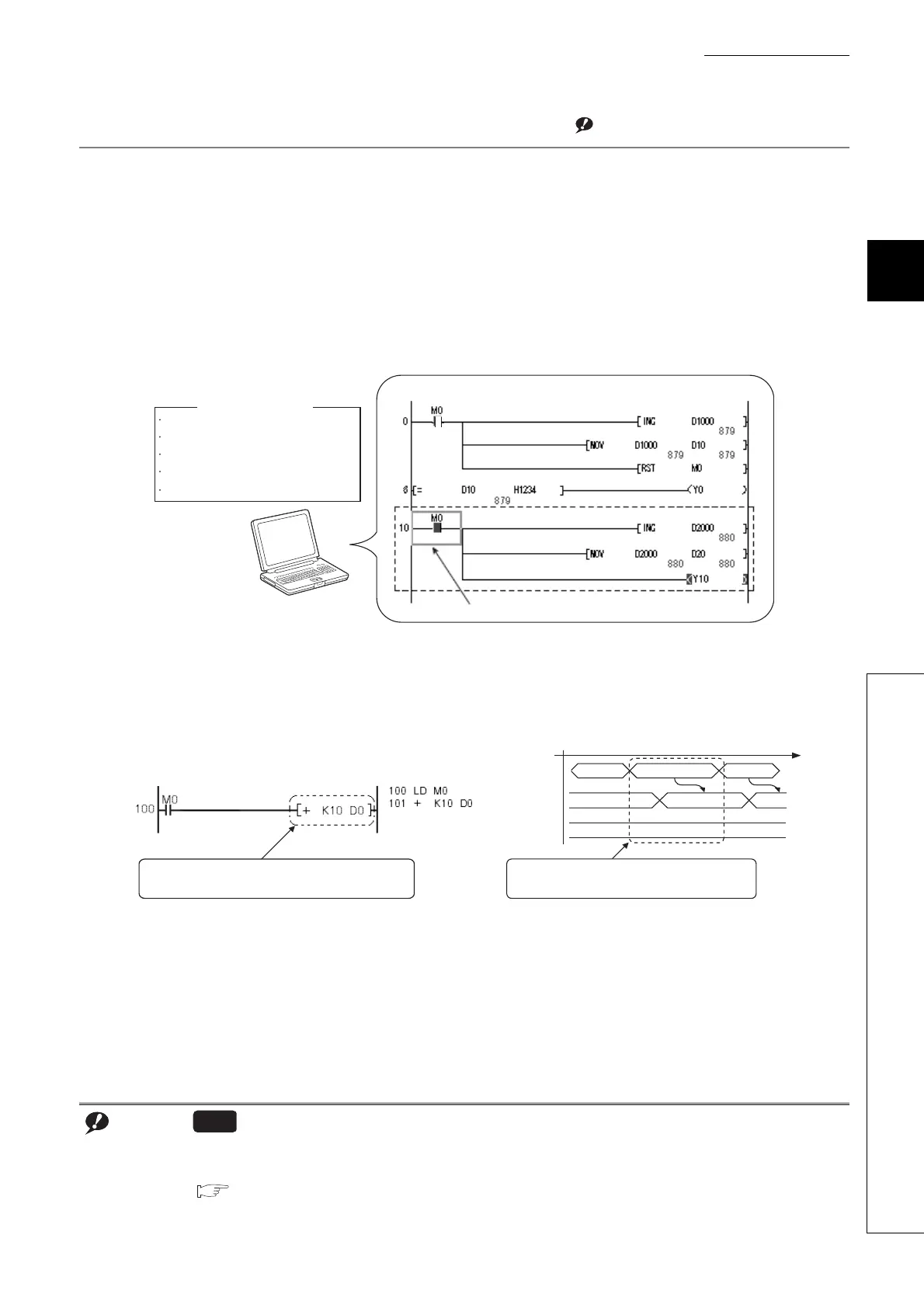

<Program example> <Operation>

Processing

LD M0

10 35

OFF

45

Changes the value in D0 to "35".

+ K10 D0

Value in D0

Value in M0

Executional conditioned device test which

sets "35" in D0 in this step is registered.

A device value is changed within the

specified step regardless of the value in M0.

List mode

Ladder mode

Loading...

Loading...