465

APPENDICES

A

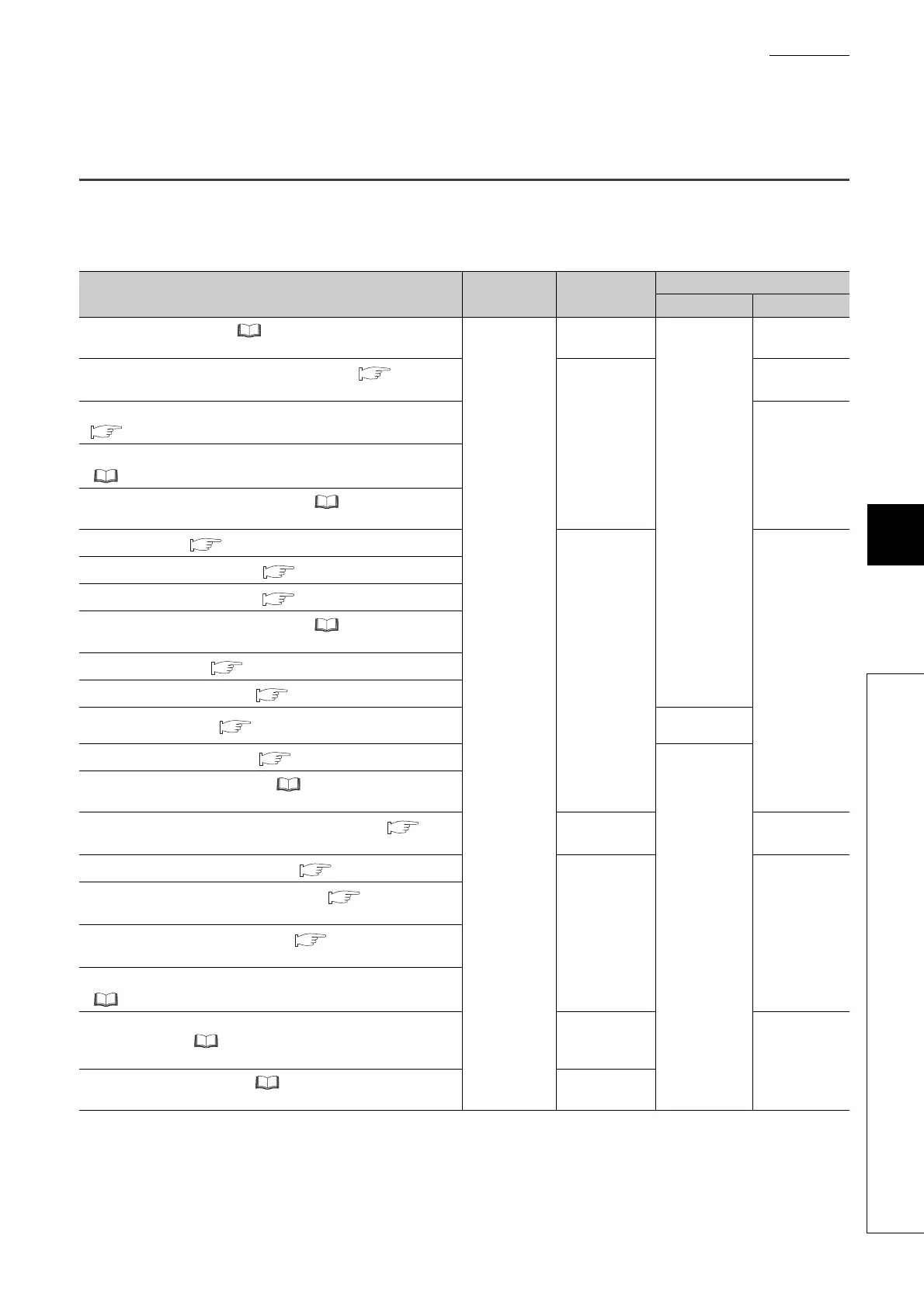

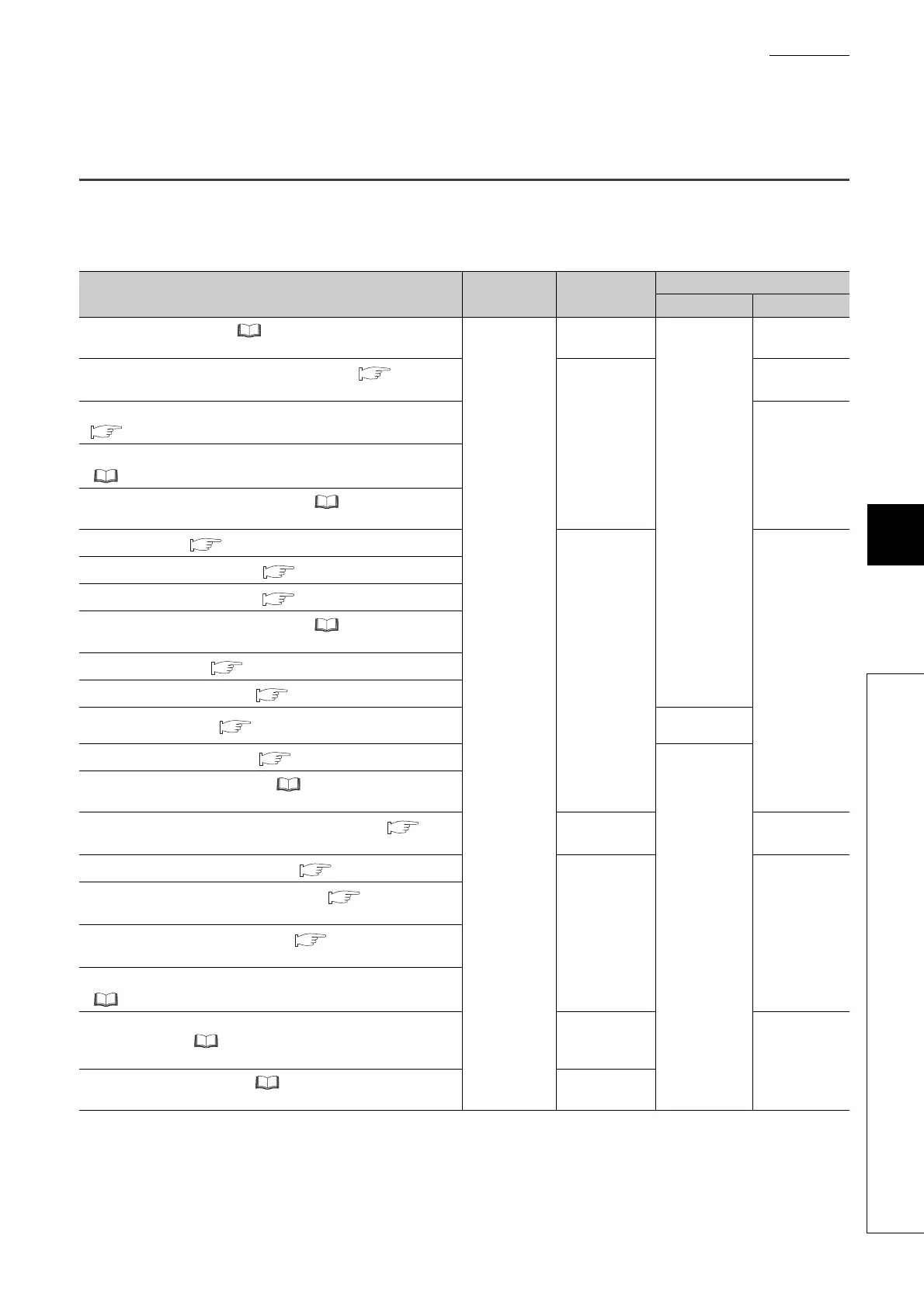

Appendix 2 Functions Added or Changed by Version Upgrade

Appendix 2 Functions Added or Changed by Version

Upgrade

The Universal model QCPU is upgraded when some functions are added or specifications are changed. Therefore, the

functions and specifications differ depending on the function version and serial number.

× : Not supported, – : Not related to the programming tool

Function

Function

version

Serial number

(first 5 digits)

Programming tool version

GX Works2 GX Developer

Use of the PC CPU module

*1

( QCPU User’s Manual (Multiple CPU

System))

B

"09072" or later

Version 1.15R

or later

–

Setting of whether to use local device for each program ( Page 420,

Section 6.2)

*6

Version 8.62Q

or later

Program memory batch transfer execution status check (SM165)

( Page 36, Section 2.1.1 (1) (d))

–

Multiple CPU high-speed transmission dedicated instruction

*1

( MELSEC-Q/L Programming Manual (Common Instruction))

Display of the amount of battery consumption ( QCPU User's Manual

(Hardware Design, Maintenance and Inspection))

Bit device extension ( Page 343, Section 4.2)

"10042" or later

Version 8.68W

or later

Executional conditioned device test ( Page 159, Section 3.11.4)

Sampling trace auto start function

*1

( Page 184, Section 3.14)

CC-Link IE group cyclic transmission function ( CC-Link IE Controller

Network Reference Manual)

Scan time measurement ( Page 181, Section 3.13.3)

External input/output forced on/off ( Page 154, Section 3.11.3)

Monitor condition setting

*1

( Page 146, Section 3.11.1)

Version 1.73B

or later

Redundant power supply system

*1

( Page 441, Appendix 1.2.4)

Version 1.15R

or later

32-bit indexing with "ZZ" specification ( MELSEC-Q/L Programming

Manual (Common Instruction))

Extended data register (D) and extended link register (W)

*1 *2

( Page

400, Section 4.8)

"09042" or later

*1

Version 8.70Y

or later

Serial communication function (Q02UCPU) ( Page 232, Section 3.23)

"10102" or later

Version 8.76E

or later

CPU module change function with memory card

*1

( Page 259, Section

3.31)

Local device setting of the index register

*1

( Page 446, Appendix

1.2.8)

Communication using the A-compatible 1C/1E frame (MC protocol)

*3 *4

( MELSEC Communication Protocol Reference Manual)

A QnA converted special relay/special register (SM1000 to SM1255,

SD1000 to SD1255) ( QCPU User's Manual (Hardware Design,

Maintenance and Inspection))

"10102" or later

Version 8.78G

or later

Socket communication function

*1

( QnUCPU User's Manual

(Communication via Built-in Ethernet Port))

"11012" or later

Loading...

Loading...