Clock-Generating Circuit

M30240 Group

Rev.1.00 Sep 24, 2003 Page 24 of 360

• fAD

This clock has the same frequency as the main clock and is used for A-D conversion.

• fUSB

This is the 48mHz clock that is used for USB operation. This clock is generated from the main clock

by the frequency synthesizer circuit.

1.2.6.3 Clock Output

In single-chip mode, the clock output function select bits (bits 0 and 1 at address 0006

16

) enable f8 or

f32 to be output from the P37/CLK

OUT

pin. When the WAIT peripheral function clock stop bit (bit 2 at

address 0006

16

) is set to “1”, the output of f8 and f32 stops when a WAIT instruction is executed.

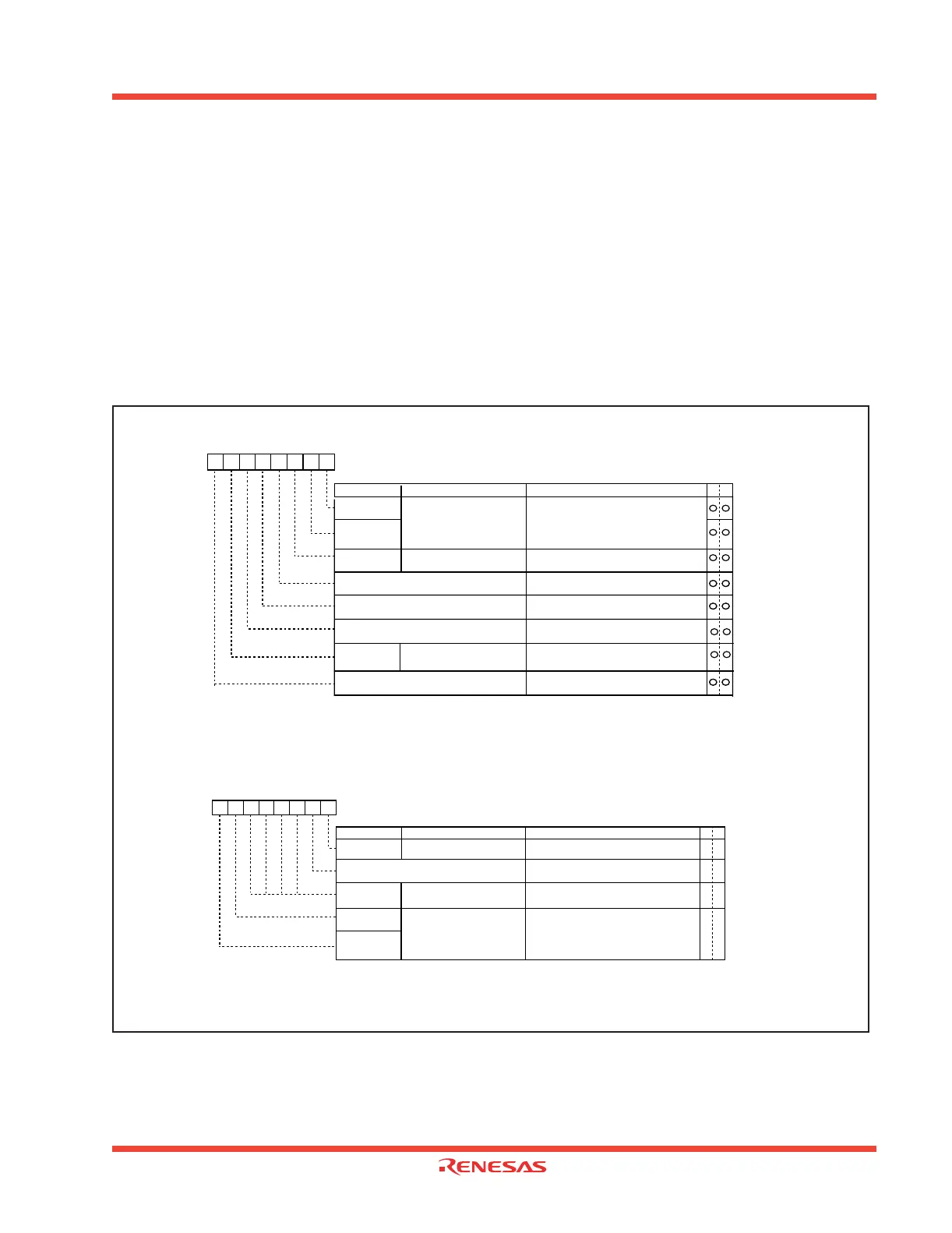

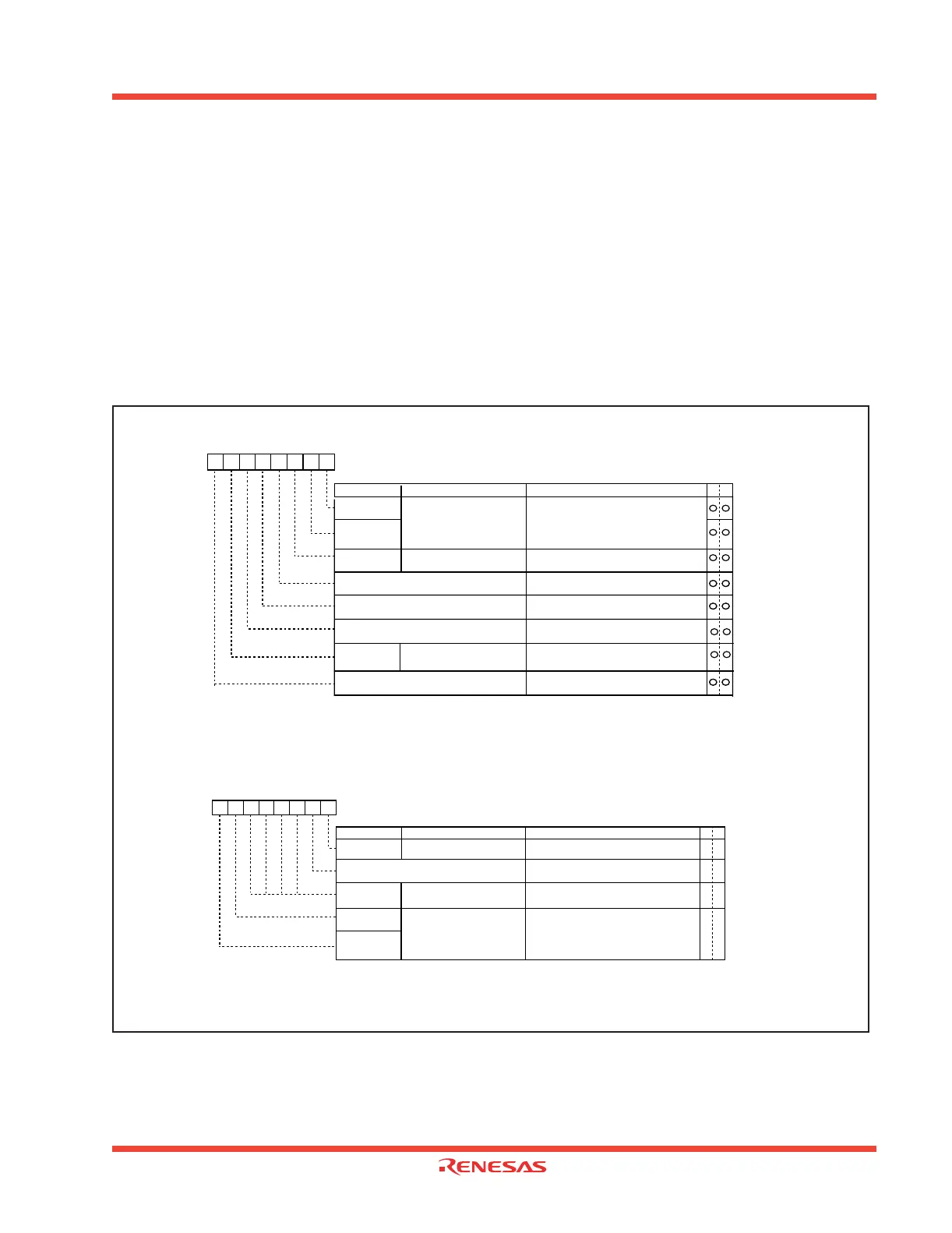

Figure 1.13 shows the system clock control registers 0 and 1.

Figure 1.13: System clock control registers 0 and 1

System clock control register 0 (Note 1)

System clock control register 1 (Note 1)

Symbol Address When reset

CM1 0007

16

20

16

Bit name FunctionBit symbol

b7 b6 b5 b4 b3 b2 b1 b0

CM10 All clock stop control bit

0 : Clock on

1 : All clocks off (stop mode)

CM15

X

IN

-X

OUT

drive capacity

select bit (Note 2)

0 : LOW

1 : HIGH

WR

CM16

CM17

Main clock division select

bit 1 (Note 3)

0 0 : No division mode

0 1 : Division by 2 mode

1 0 : Division by 4 mode

1 1 : Division by 16 mode

b7 b6

00

Reserved bit

Always set to

“0”

00

Symbol Address When reset

CM0 0006

16

48

16

Bit name FunctionBit symbol

b7 b6 b5 b4 b3 b2 b1 b0

0 0 : I/O port P37

0 1 : Invalid

1 0 : f

8 output

1 1 : f

32 output

b1 b0

CM01

CM02

CM00

Clock output function

select bit

WAIT peripheral function

clock stop bit

0 : Do not stop f1, f8, f32 in wait mode

1 : Stop f

1, f8, f32 in wait mode

WR

CM06

Main clock division select

bit 0 (Note 2)

0 : CM16 and CM17 valid

1 : Division by 8 mode

Reserved bit

Always set to "1"

Reserved bit

Always set to "0"

Reserved bit

Always set to "0"

Reserved bit

Always set to "0"

o

o

o

o

o

o

o

o

Note 1: Set bit 0 of the Protect register (address 000A

16

) to "1" before writing to this register.

Note 2: Changes to "1" when shifting to stop mode.

Note 3: Can be selected when bit 6 of the System clock control register 0 (address 0006

16

) is "0".

If "1", division mode is fiixed at "8".

Note 1: Set bit 0 of the Protect register (address 000A

16

) to "1" before writing to this register.

Note 2: Changes to "1" when shifting to stop mode.

Loading...

Loading...