RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1258

Dec 10, 2015

17.9 Interrupts

The LIN/UART module generates four types of interrupt requests.

LINn successful transmission interrupt

LINn successful reception interrupt

LINn reception status interrupt

LINn interrupt

Setting the LIOS bit in the LMDn register to 0 allows to perform logical OR operation on all of the interrupt sources, outputting

the interrupt request from the LINn interrupt.

Setting the LIOS bit in the LMDn register to 1 allows to output the LINn successful transmission interrupt, LINn successful

reception interrupt, or LINn reception status interrupt depending on the interrupt sources.

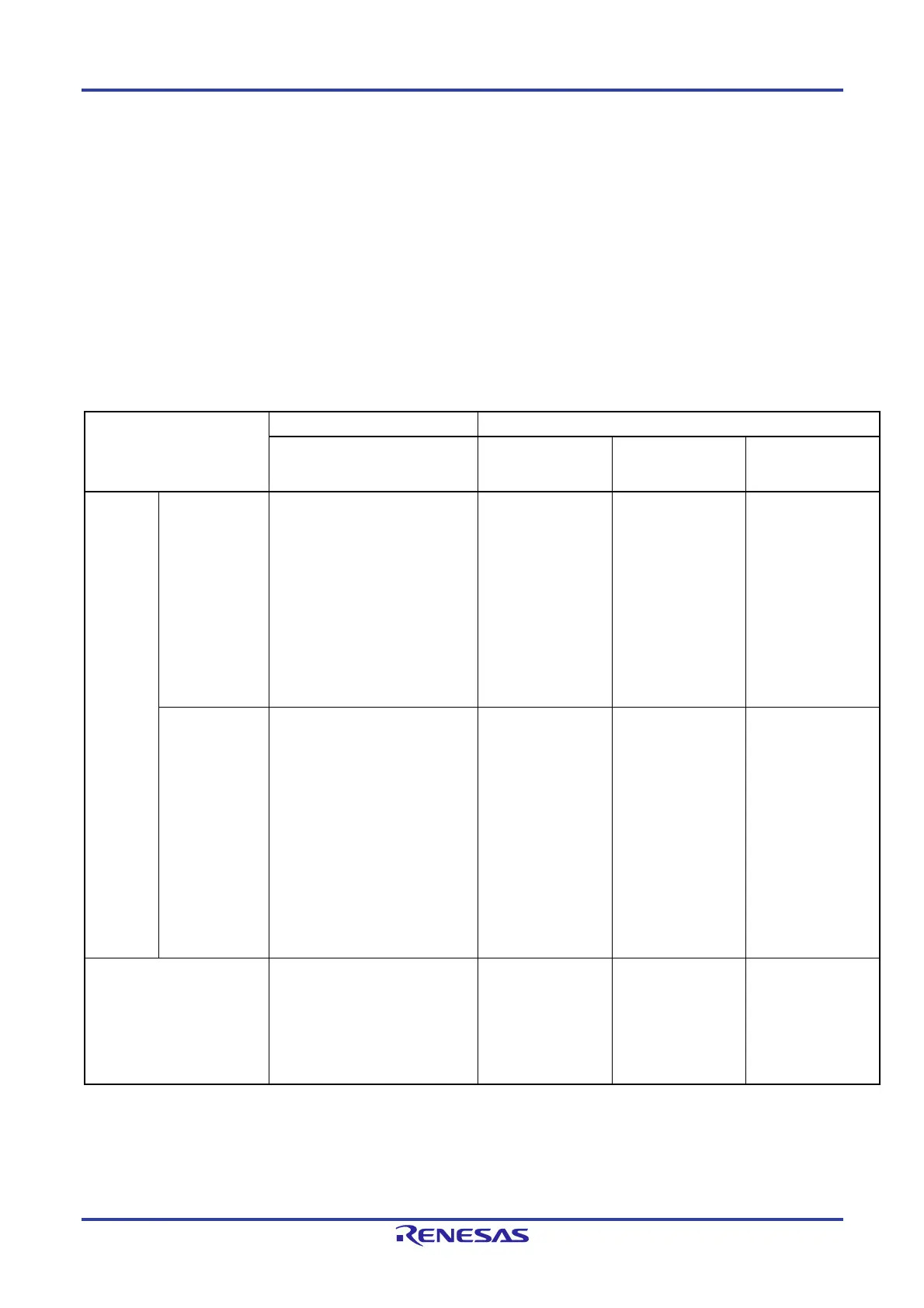

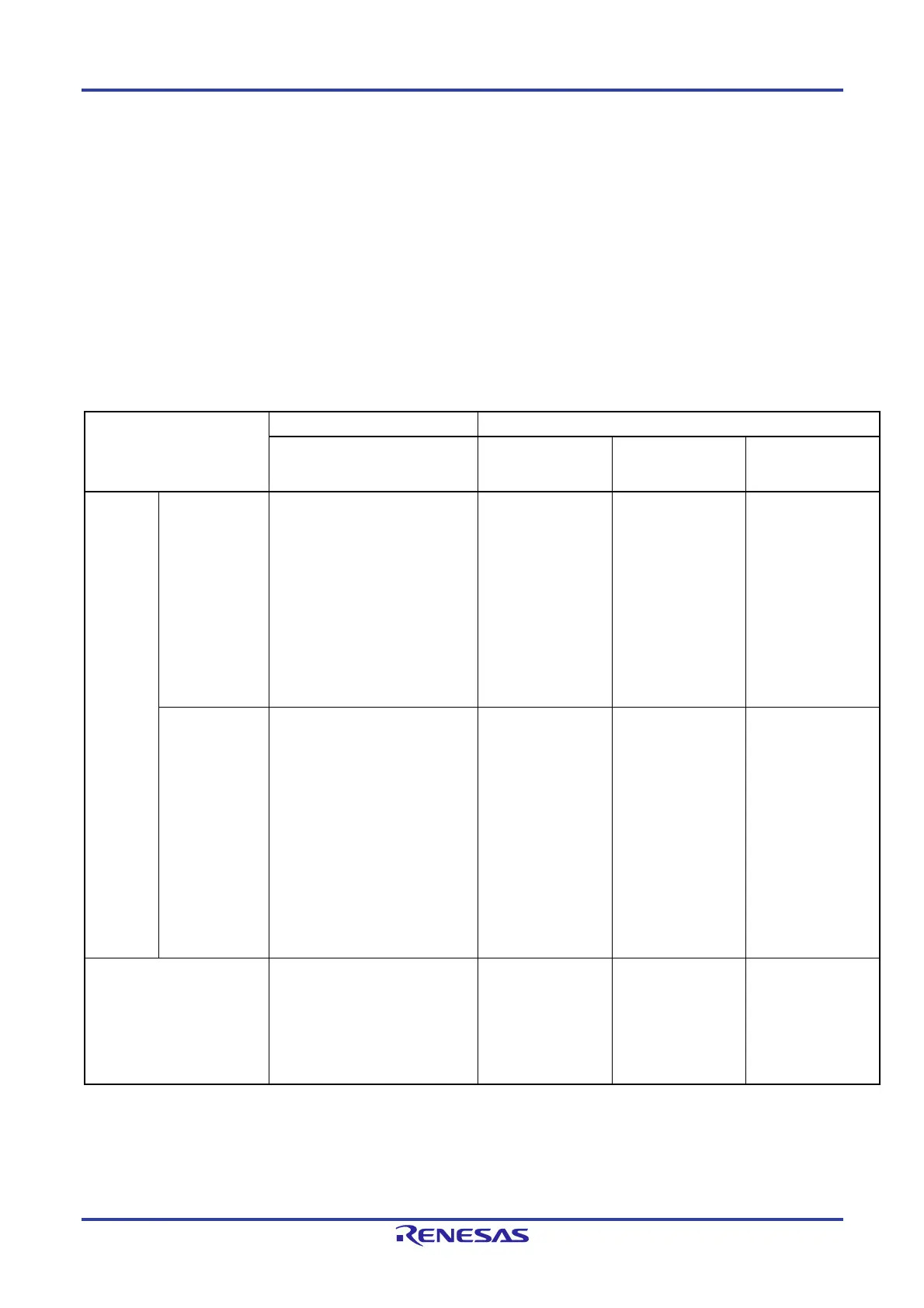

Table 17-31 lists the sources for each interrupt.

Table 17-31. Interrupt Sources

Mode

LIOS bit in LMDn register is 0 LIOS bit in LMDn register is 1

Note

LINn Interrupt

LINn Successful

Transmission

Interrupt

LINn Successful

Reception Interrupt

LINn Reception

Status Interrupt

LIN mode LIN

master mode

Successful frame transmission

Successful frame reception

Successful wake-up

transmission

Successful wake-up reception

Successful header transmission

Bit error

Physical bus error

Frame/response timeout error

Framing error

Checksum error

Response preparation error

Successful frame

transmission

Successful wake-

up transmission

Successful header

transmission

Successful frame

reception

Successful wake-

up reception

Bit error

Physical bus error

Frame/response

timeout error

Framing error

Checksum error

Response

preparation error

LIN

slave mode

Successful response

transmission

Successful response reception

Successful wake-up

transmission

Successful wake-up reception

Successful header reception

Bit error

Frame/response timeout error

Framing error

Sync field error

Checksum error

ID parity error

Response preparation error

Successful

response

transmission

Successful wake-

up transmission

Successful

response

reception

Successful wake-

up reception

Successful header

reception

Bit error

Frame/response

timeout error

Framing error

Sync field error

Checksum error

ID parity error

Response

preparation error

UART mode ― Transmission

start/successful

transmission

Successful

reception

Expansion bit

mismatch

Bit error

Overrun error

Framing error

Expansion bit

detection

ID match

Parity error

Note LIOS bit setting is enabled in LIN mode. LIOS bit setting is not required in UART mode.

Each interrupt request is output when the corresponding bit in the LIEn register is 1 (interrupt is enabled) and the

corresponding flag in the LSTn register is 1.

In the RL78/F13 and RL78/F14, the LINn reception status interrupt and LINn interrupt are assigned to the same interrupt

vector.

Loading...

Loading...