RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1412

Dec 10, 2015

18.11.2 FIFO Buffer Reading Procedure

When received messages have been stored in one or more receive FIFO buffers or a transmit/receive FIFO buffer that

is set to receive mode, the corresponding message count display counter (RFMC[5:0] bits in the RFSTSm register (m = 0,

1) or CFMC[5:0] bits in the CFSTSk register) is incremented. At this time, when the RFIE bit (receive FIFO interrupt is

enabled) in the RFCCm register or the CFRXIE bit (transmit/receive FIFO receive interrupt is enabled) in the CFCCLk

register is set to 1, an interrupt request is generated. Received messages can be read from the RFIDLm, RFIDHm,

RFTSm, RFPTRm, and RFDF0m to RFDF3m registers (receive FIFO buffers) or the CFIDLk, CFIDHk, CFTSk, CFPTRk,

and CFDF0k to CFDF3k registers (transmit/receive FIFO buffers). Messages in FIFO buffers can be read sequentially on

a first-in, first-out basis.

When the message count display counter value matches the FIFO buffer depth (a value set by the RFDC[2:0] bits in

the RFCCm register or the CFDC[2:0] bits in the CFCCLk register), the RFFLL or CFFLL flag is set to 1 (the receive FIFO

buffer is full).

When all messages have been read out of the FIFO buffer, the RFEMP flag in the RFSTSm register or the CFEMP flag

in the CFSTSk register is set to 1 (the receive FIFO buffer contains no unread message (buffer empty)).

If the RFE bit or the CFE bit is cleared to 0 (no receive FIFO buffer is used) with the interrupt request flag (RFIF flag in

the RFSTSm register or CFRXIF flag in the CFSTSk register) set to 1 (a receive FIFO interrupt request is present), the

interrupt request flag is not automatically cleared to 0. Clear the interrupt request flag to 0 by the program.

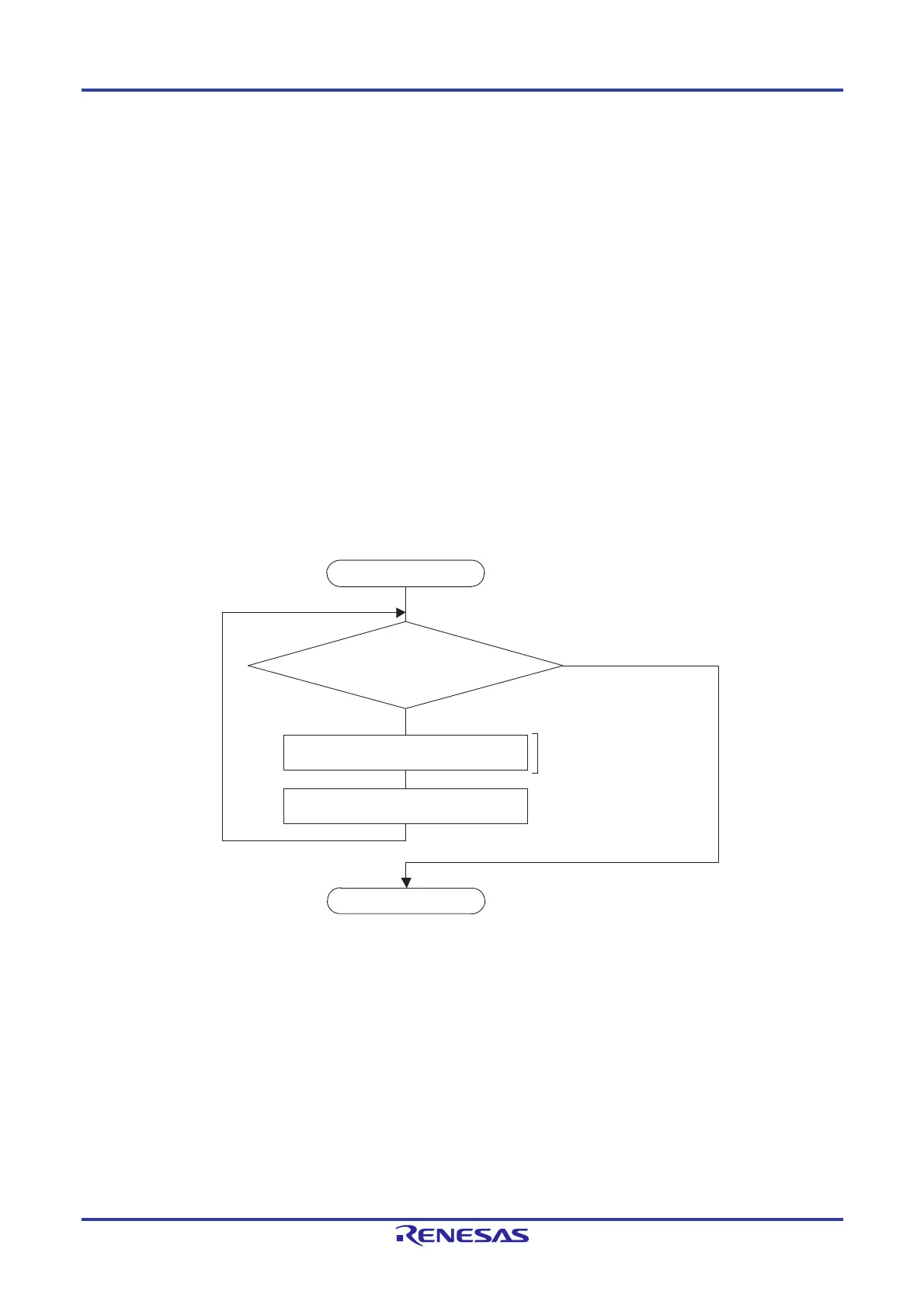

Figure 18-24. Transmit/Receive FIFO Buffer Reading Procedure

End

No

Yes

Remark k = 0

Set the CFPCTRk register to H'FF.

Read messages from registers CFIDLk, CFIDHk, CFTSk,

CFPTRk, and CFDF0k to CFDF3k.

Start

Read messages when the RPAGE bit

in the GRWCR register is set to 1.

Is transmit/receive FIFO buffer empty?

(Is the CFEMP bit in the CFSTSk register 1?)

Loading...

Loading...