RL78/F13, F14 CHAPTER 5 CLOCK GENERATOR

R01UH0368EJ0210 Rev.2.10 405

Dec 10, 2015

5.6.3 Example of Setting XT1 Oscillator

After a reset release, the CPU/peripheral hardware clock (f

CLK) always starts operating with the high-speed on-chip

oscillator clock. To subsequently change the clock to the XT1 oscillation clock, set the oscillator and start oscillation by

using the operation speed mode control register (OSMC), clock select register (CKSEL), clock operation mode control

register (CMC), and clock operation status control register (CSC), set the XT1 oscillation clock to f

CLK by using the system

clock control register (CKC).

[Register settings] Set the registers in the following order.

<1> The RTCLPC bit in the OSMC register can be used to enable or disable supply of the clock to the peripheral functions

in STOP mode or HALT mode while sub/low-speed on-chip oscillator selection clock is selected as CPU clock.

When RTCLPC = 0, the supply of the subsystem/low-speed on-chip oscillator select clock to peripheral functions is

enabled. When RTCLPC = 1, the supply of the subsystem/low-speed on-chip oscillator select clock to peripheral

functions except for the real-time clock is stopped.

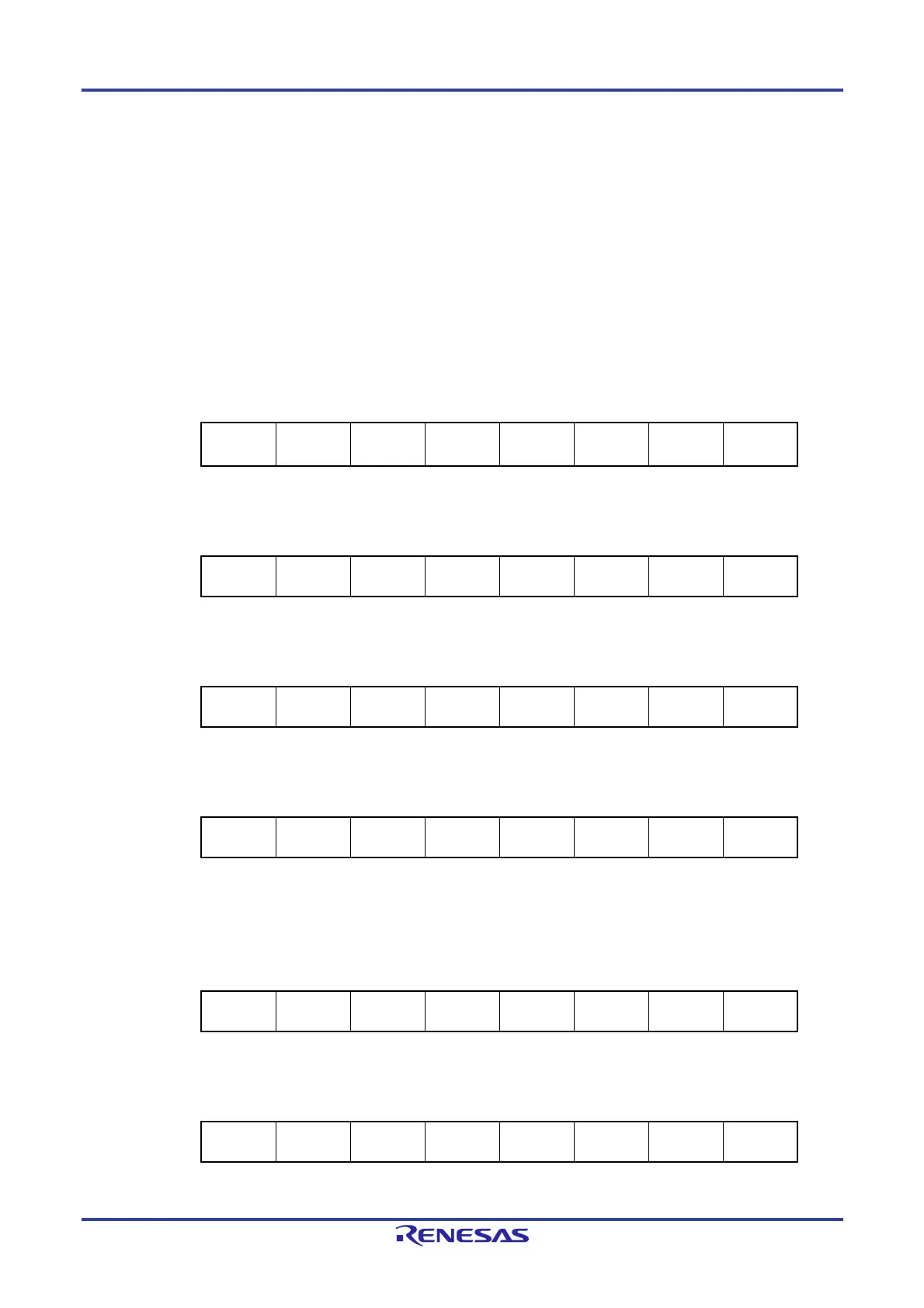

7 6 5 4 3 2 1 0

OSMC

RTCLPC

0/1

0

0

WUTMMCK0

0

0

0

0

0

<2> Select f

SUB with the SELLOSC bit of the CKSEL register.

Clear the SELLOSC bit to 0 to set f

SL to the XT1 oscillation clock.

7 6 5 4 3 2 1 0

CKSEL

0

0

0

0

0

TRD_CKSEL

0

0

SELLOSC

0

<3> Select the operation mode of the subsystem clock with the OSCSELS bit of the CMC register.

Set the OSCSELS bit to 1 to select the XT1 oscillation mode or external clock input mode.

7 6 5 4 3 2 1 0

CMC

EXCLK

0

OSCSEL

0

EXCLKS

0

OSCSELS

1

0

AMPHS1

0/1

AMPHS0

0/1

AMPH

0

AMPHS0 and AMPHS1 bits: These bits are used to specify the oscillation mode of the XT1 oscillator.

<4> Clear the XTSTOP bit of the CSC register to 0 to start oscillating the XT1 oscillator.

7 6 5 4 3 2 1 0

CSC

MSTOP

0

XTSTOP

0

0

0

0

0

0

HIOSTOP

0

<5> Use the timer function or another function to wait for oscillation of the subsystem clock to stabilize by using software.

<6> Select the CPU/peripheral hardware clock with the CSS bit of the CKC register.

Set the CSS bit to 1 to specify CPU clock = f

SL (XT1 oscillation clock).

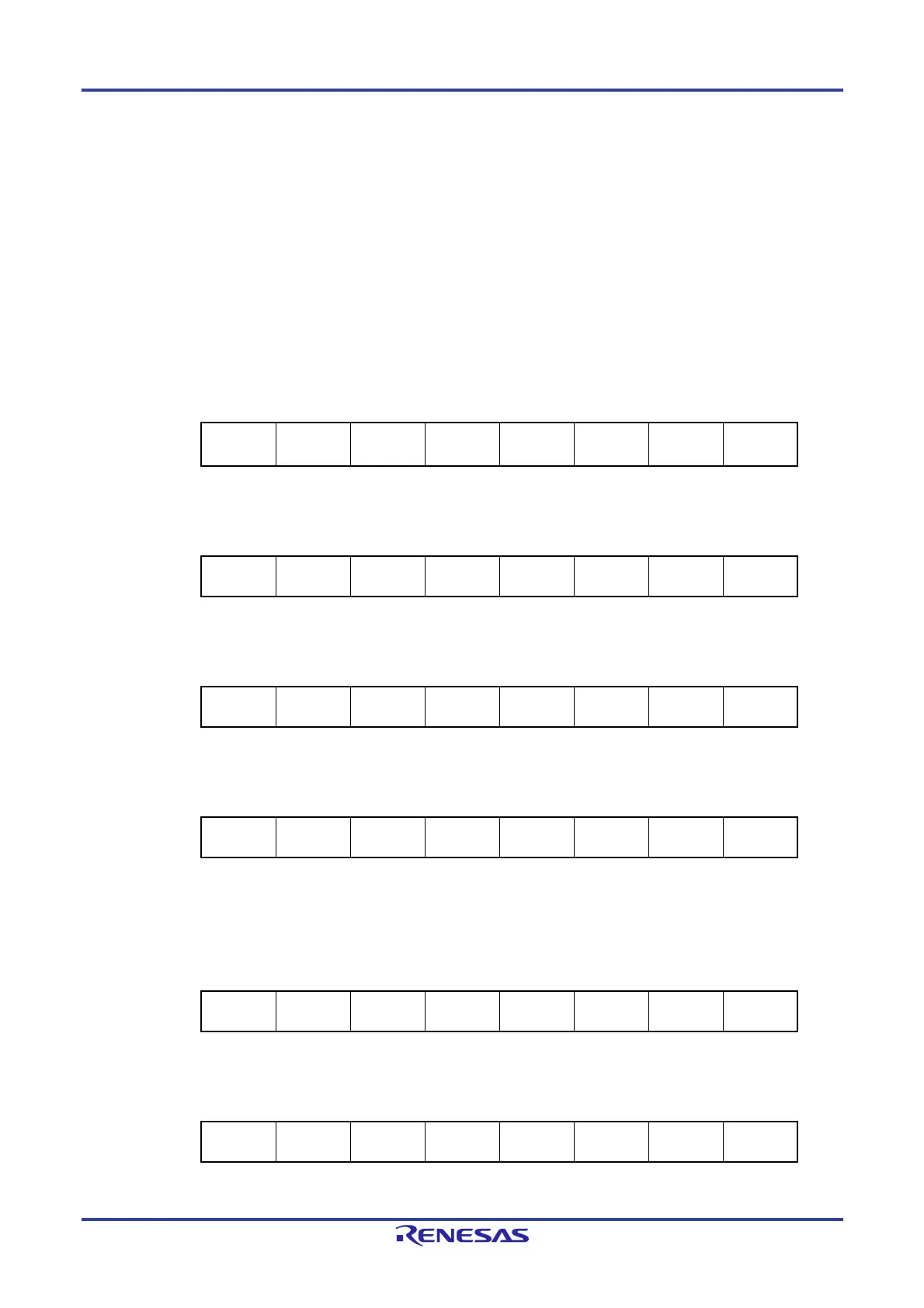

7 6 5 4 3 2 1 0

CKC

CLS

0

CSS

1

MCS

0

MCM0

0

0

0

0

0

<7> Confirm that f

SL (XT1 oscillation clock) is selected as the CPU/peripheral hardware clock (CLS = 1) with the CLS bit

of the CKC register.

7 6 5 4 3 2 1 0

CKC

CLS

1

CSS

1

MCS

0

MCM0

0

0

0

0

0

Loading...

Loading...