RL78/F13, F14 CHAPTER 35 ELECTRICAL SPECIFICATIONS (GRADE K)

R01UH0368EJ0210 Rev.2.10 1743

Dec 10, 2015

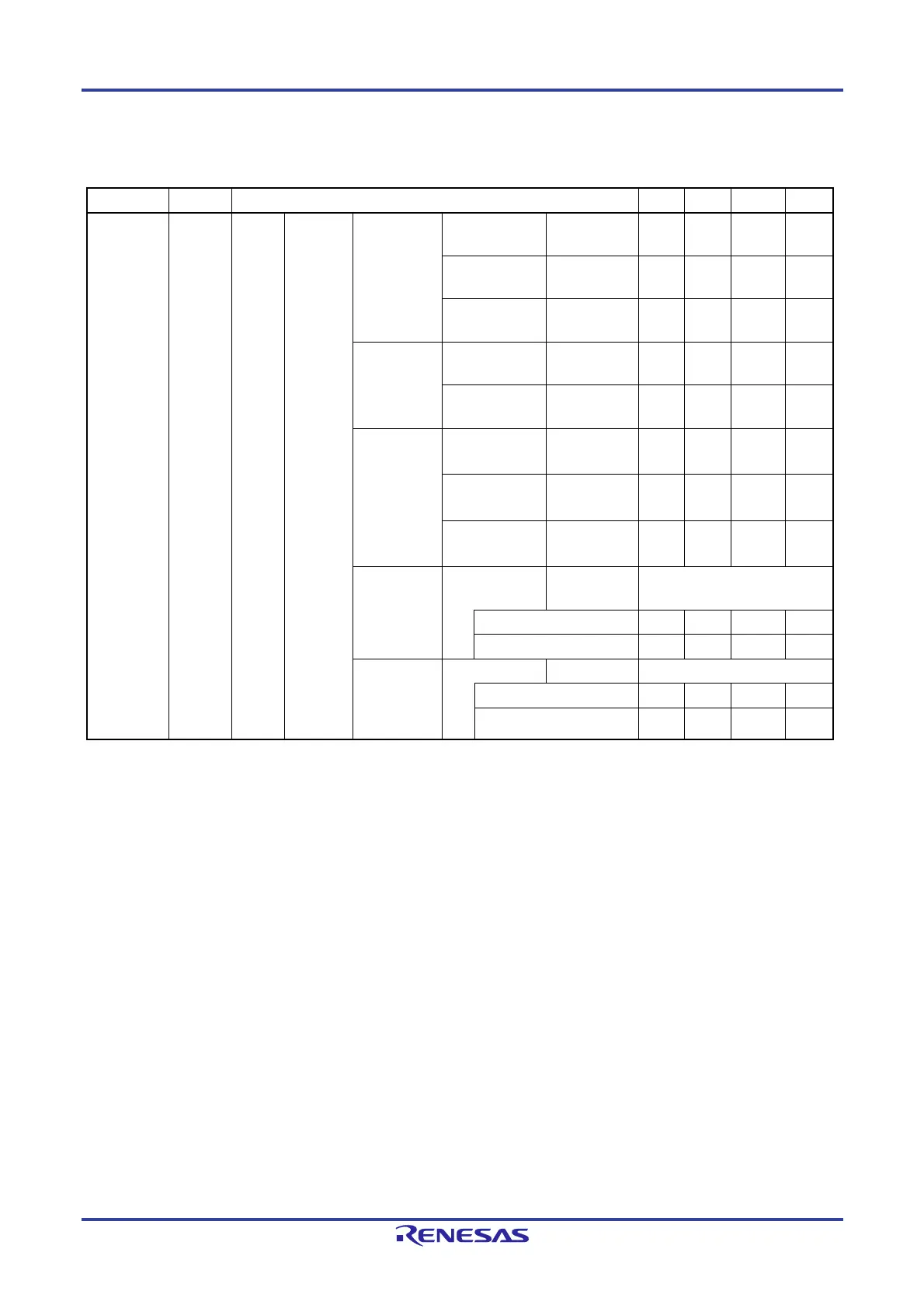

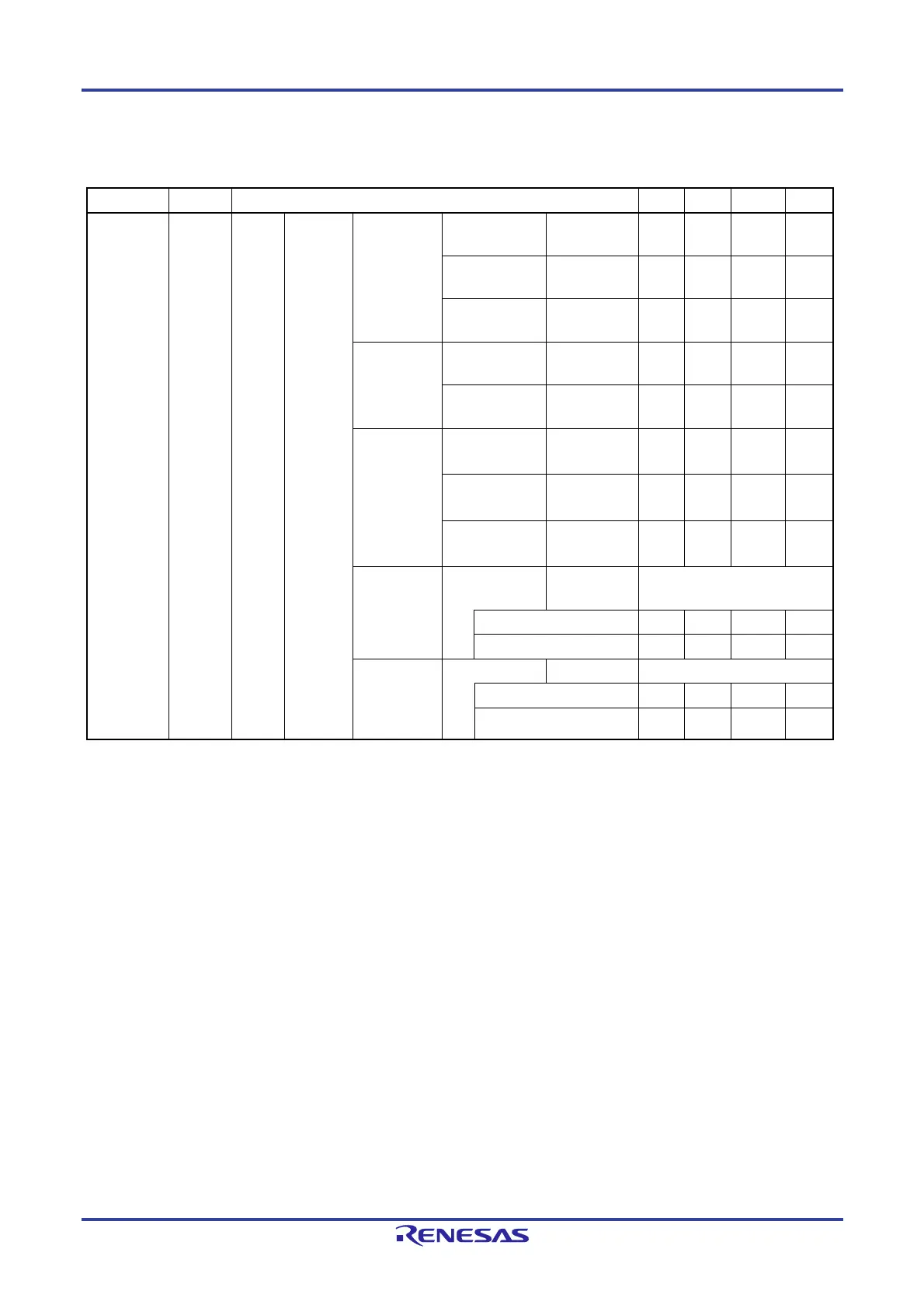

35.3.2 Supply Current Characteristics

(TA = -40 to +125C, 2.7 V EVDD0 = EVDD1 = VDD 5.5 V, VSS = EVSS0 = EVSS1 = 0 V) (1/3)

Items Symbol Conditions MIN. TYP. MAX. Unit

Supply

current

Note 1

I

DD1

Operating

mode

Normal

operation

Note 2

High-speed

on-chip

oscillator clock

operation

f

IH = 48 MHz

f

CLK = 24 MHz

Notes 3, 4

5.1 12.0 mA

fIH = 24 MHz

f

CLK = fIH

Notes 3,

4

4.8 11.0 mA

fIH = 1 MHz

f

CLK = fIH

Notes 3,

4

1.0 2.5 mA

Resonator

operation

f

MX = 20 MHz

f

CLK = fMX

Notes

3, 5

4.2 9.0 mA

fMX = 1 MHz

f

CLK = fMX

Notes

3, 5

0.9 2.5 mA

Resonator

operation

(PLL

operation)

(PLL input

clock = f

MX)

f

PLL = 48 MHz,

f

MX = 8 MHz

f

CLK = 24 MHz

Notes 3, 6

5.0 12.0 mA

fPLL = 24 MHz,

f

MX = 8 MHz

f

CLK = 24 MHz

Notes 3, 6

4.9 11.0 mA

fPLL = 24 MHz,

f

MX = 4 MHz

f

CLK = 24 MHz

Notes 3, 6

4.7 11.0 mA

Subsystem

clock

operation

f

SUB = 32.768

kHz

f

CLK = fSUB

Note 7

Groups A to D 6.0 80.0 A

Group E 6.0 120.0 A

Low-speed

on-chip

oscillator clock

operation

f

IL = 15 kHz fCLK = fIL

Note 8

Groups A to D 3.0 70.0 A

Group E 3.0 110.0 A

Notes 1. Total current flowing into VDD and EVDD0, including the input leakage current flowing when the level of the

input pin is fixed to V

DD, EVDD0, VSS, or EVSS0. However, not including the current flowing into the I/O buffer and

on-chip pull-up/pull-down resistors.

2. Current drawn when all the CPU instructions are executed.

3. The values below the MAX. column include the peripheral operation current (except for background

operation (BGO)). However, the LVD circuit, A/D converter, D/A converter, and comparator are stopped.

4. When high-speed system clock, subsystem clock, PLL clock, and low-speed on-chip oscillator clock are

stopped.

5. When subsystem clock, PLL clock, high-speed on-chip oscillator clock, and low-speed on-chip oscillator

clock are stopped.

6. When subsystem clock, high-speed on-chip oscillator clock, and low-speed on-chip oscillator clock are

stopped.

7. When high-speed system clock, PLL clock, high-speed on-chip oscillator clock, and low-speed on-chip

oscillator are stopped.

8. When high-speed system clock, subsystem clock, PLL clock, and high-speed on-chip oscillator clock are

stopped.

Remarks 1. f

MX: High-speed system clock frequency

2. f

SUB: Subsystem clock frequency

3. f

PLL: PLL clock frequency

4. fIH: High-speed on-chip oscillator clock frequency

5. f

IL: Low-speed on-chip oscillator clock frequency

6.

fCLK: CPU/peripheral hardware clock frequency

Loading...

Loading...