RL78/F13, F14 CHAPTER 27 SAFETY FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1600

Dec 10, 2015

(2) Starting and stopping of operation

Bit 4 (CLKMB) of the option byte (000C1H) should be set to 0 to enable operation of the clock monitor.

After the oscillation of the low-speed on-chip oscillator is set, the clock monitor starts operation.

The clock monitor automatically stops operating under the following conditions.

In STOP mode

In SNOOZE mode

During counting of the oscillation stabilization time after STOP mode was released

When the CPU/peripheral hardware clock frequency (f

CLK) is equal to the subsystem clock (fSUB) or low-speed on-

chip oscillator clock (f

IL)

When the sampling clock is stopped (low-speed on-chip oscillator is stopped)

When bit 4 (CLKMB) of the option byte (000C1H) is 1

(3) Cautions for use

When entering the STOP mode by stopping the PLL clock during the operation of the clock monitor, set bit 0 (PLLON)

in the PLL control register (PLLCTL) before executing the STOP instruction.

27.3.6 RAM guard function

This RAM guard function is used to protect data in the specified memory space.

If the RAM guard function is specified, writing to the specified RAM space is disabled, but reading from the space can be

carried out as usual. The area used as the stack must not be a target of the RAM guard function.

<Control register>

(1) Invalid memory access detection control register (IAWCTL)

This register is used to control the detection of invalid memory access and RAM/SFR guard function.

GRAM1 and GRAM0 bits are used in RAM guard function.

The IAWCTL register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

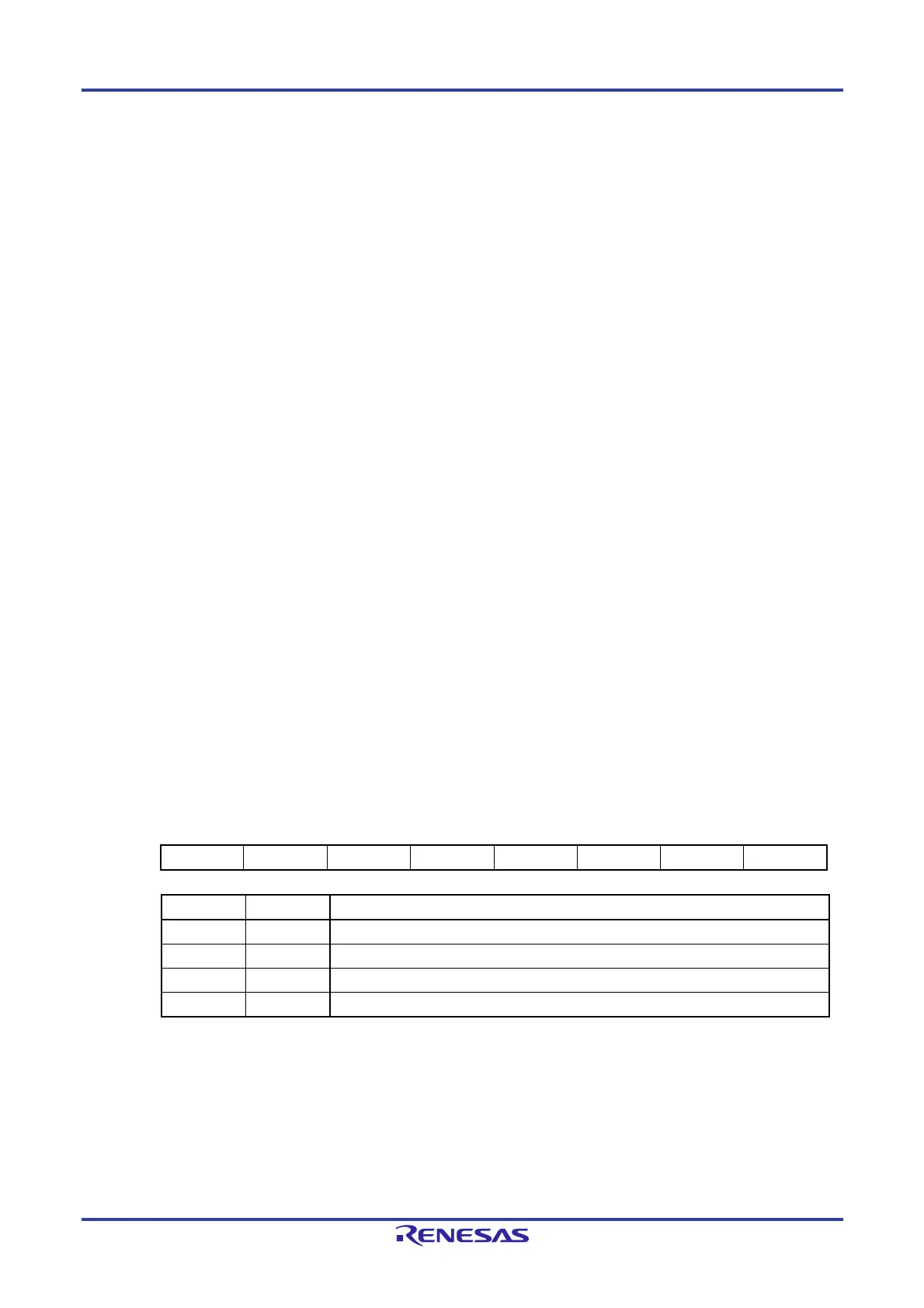

Figure 27-19. Format of Invalid Memory Access Detection Control Register (IAWCTL)

Address: F0078H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

IAWCTL IAWEN 0 GRAM1 GRAM0 0 GPORT GINT GCSC

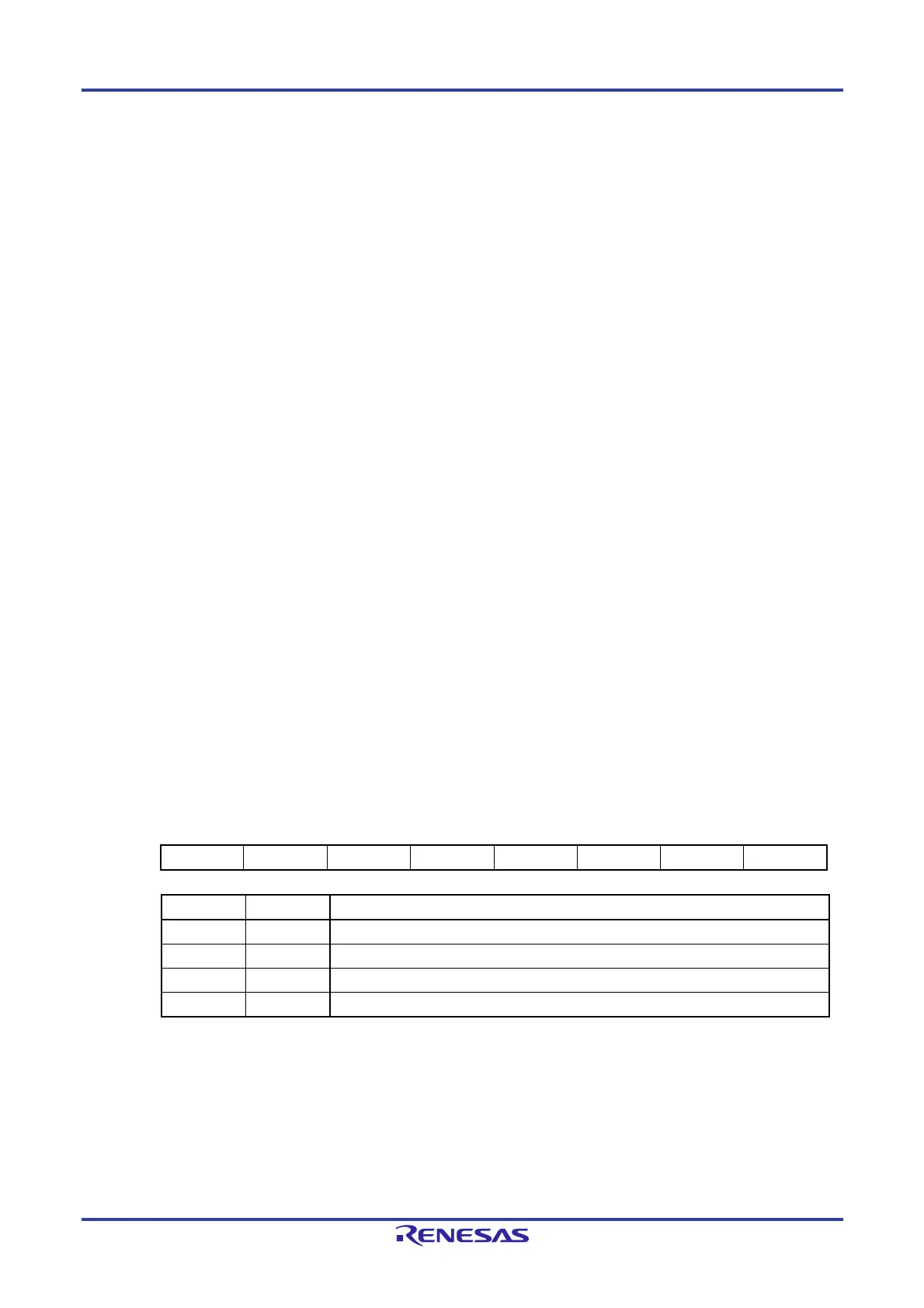

GRAM1 GRAM0 RAM guard space

Note

0 0 Disabled. RAM can be written to.

0 1 The 128 bytes starting at the lower RAM address

1 0 The 256 bytes starting at the lower RAM address

1 1 The 512 bytes starting at the lower RAM address

Note Do not set the RAM guard space to an area exceeding the size of the RAM of the product.

Loading...

Loading...