RL78/F13, F14 CHAPTER 36 ELECTRICAL SPECIFICATIONS (GRADE Y)

R01UH0368EJ0210 Rev.2.10 1830

Dec 10, 2015

36.7 Power Supply Voltage Rising Time

(TA = -40 to +150C, VSS = EVSS0 = EVSS1 = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Maximum power supply

voltage rising slope

S

vrmax

0 V V

DD (VPOC2 = 0 or 1

Note 2

)

50

Note 3

V/ms

Minimum power supply voltage

rising slope

Note 1

S

vrmin 0 V 2.7 V 6.5 V/ms

Notes 1. The minimum power supply voltage rising slope is applied only under the following condition.

When the voltage detection (LVD) circuit is not used (VPOC2 = 1) and an external reset circuit is not used or

when a reset is not effected until VDD = 2.7 V.

2. These values indicate setting values of option bytes.

3. If the power supply drops below VPDR and a POR reset is effected, this specification is also applied when the

power supply is recovered without dropping to 0 V.

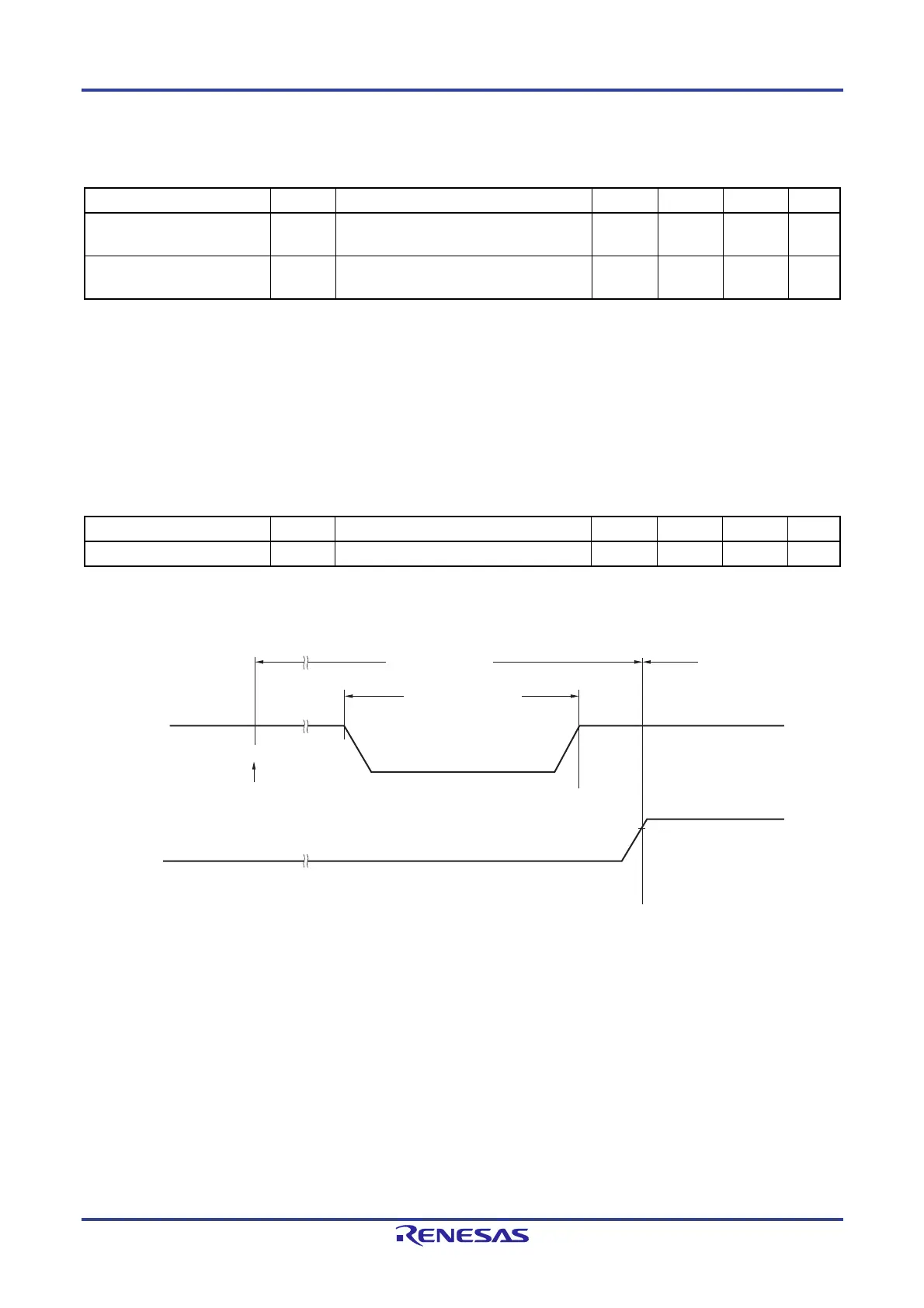

36.8 STOP Mode Memory Retention Characteristics

(TA = -40 to +150C, VSS = EVSS0 = EVSS1 = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Data retention supply voltage VDDDR

1.47

Note

5.5 V

Note The value depends on the POR detection voltage. When the voltage drops, the data is retained before a POR

reset is effected, but data is not retained when a POR reset is effected.

VDD

STOP instruction execution

Standby release signal

(interrupt request)

STOP mode

Data retention mode

V

DDDR

Operation mode

Loading...

Loading...