RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1388

Dec 10, 2015

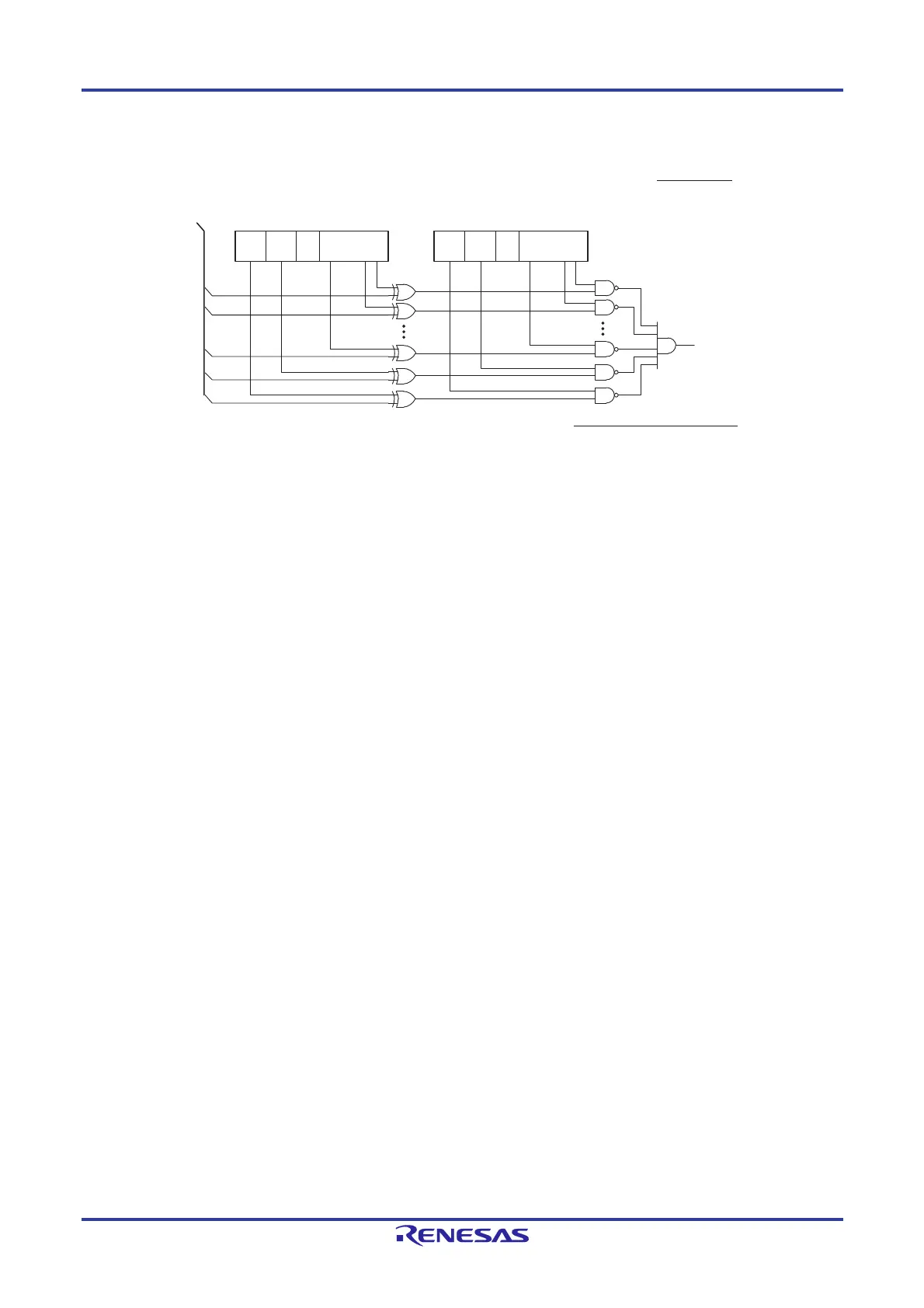

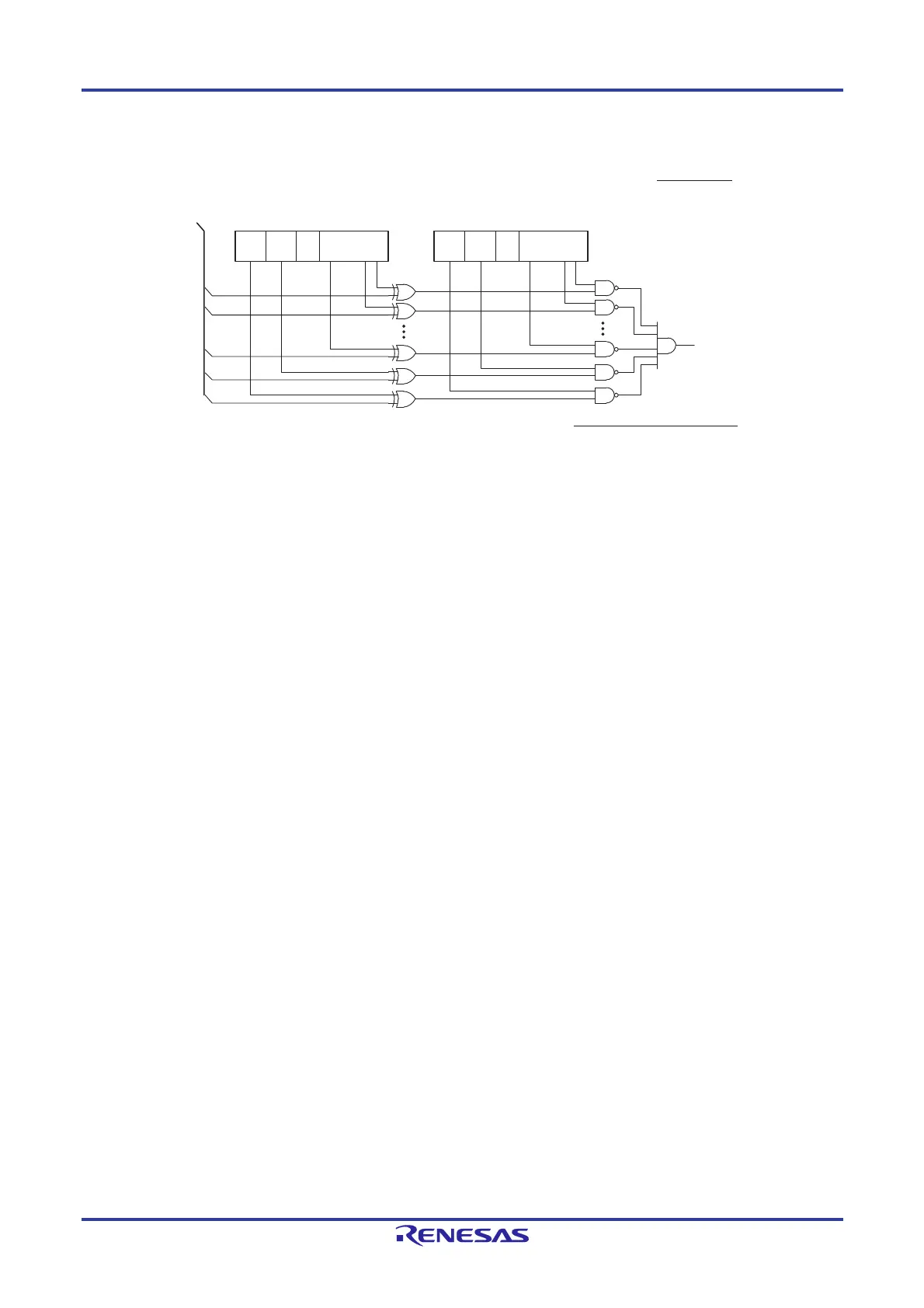

Figure 18-5. Acceptance Filter Function

(2) DLC Filter Processing

When the DCE bit in the GCFGL register is set to 1 (DLC check is enabled), DLC filter processing is added to

messages that passed through the acceptance filter processing. When the DLC value in a message is equal to or larger

than the DLC value set in the receive rule, the message passes through the DLC filter processing.

When a message has passed through the DLC filter processing with the DRE bit in the GCFGL register set to 0 (DLC

replacement is disabled), the DLC value in the received message is stored in the buffer. In this case, all the data bytes in

the received message are stored in the buffer.

When a message has passed through the DLC filter processing with the DRE bit in the GCFGL register set to 1 (DLC

replacement is enabled), the DLC value in the receive rule is stored in the buffer instead of the DLC value in the received

message. In this case, a value of H'00 is written to data bytes that are larger than the DLC value in the receive rule.

When the DLC value in the received message is smaller than that in the receive rule, the message does not pass

through the DLC filter processing. In this case, the message is not stored in the receive buffer or the FIFO buffer and the

DEF flag in the GERFLL register is set to 1 (a DLC error is present).

(3) Routing Processing

Messages that passed through the acceptance filter processing and the DLC filter processing are stored in receive

buffers, receive FIFO buffers, or transmit/receive FIFO buffers (set to receive mode). Message storage destination is set

by the GAFLRMV, GAFLRMDP[6:0], GAFLFDP4, and GAFLFDP[1:0] bits in the GAFLPLj register (j = 0 to 15). Messages

that passed through the acceptance filter processing and the DLC filter processing can be stored in up to two buffers.

(4) Label Addition Processing

It is possible to add 12-bit label information to messages that passed through the filter processing and store them in

buffers. This label information is set in the GAFLPTR[11:0] bits in the GAFLPHj register.

(5) Mirror Function Processing

The mirror function allows reception of messages transmitted from the own CAN node. The mirror function is made

available by setting the MME bit in the GCFGL register to 1 (mirror function is enabled).

When the mirror function is in use, receive rules for which the GAFLLB bit in the GAFLIDHj register is set to 0 are used

for data processing when receiving messages transmitted from other CAN nodes. When receiving messages transmitted

from the own CAN node, receive rules for which the GAFLLB bit is set to 1 are used for data processing.

ID value in

received

message

GAFLIDHj, GAFLIDLj

(CAN receive rule entry register jAH/AL)

GAFLMHj, GAFLMLj

(CAN receive rule entry register jBH/BL)

Mask bit value

0: Bits are not compared.

1: Bits are compared.

GAFLIDE, GAFLRTR, GAFLID: Bits in the GAFLIDHj and GAFLIDLj registers

GAFLIDEM, GAFLRTRM, GAFLIDM: Mask bits in the GAFLMHj and GAFLMLj registers

Acceptance

determination

signal

GAFLID

GAFLIDM

GAFL

IDEM

GAFL

RTRM

GAFL

IDE

GAFL

RTR

Acceptance determination signal

0: Does not pass the acceptance filter processing.

(Not stored in the buffer)

1: Passes the acceptance filter processing.

Remark j = 0 to 15

Loading...

Loading...