RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1393

Dec 10, 2015

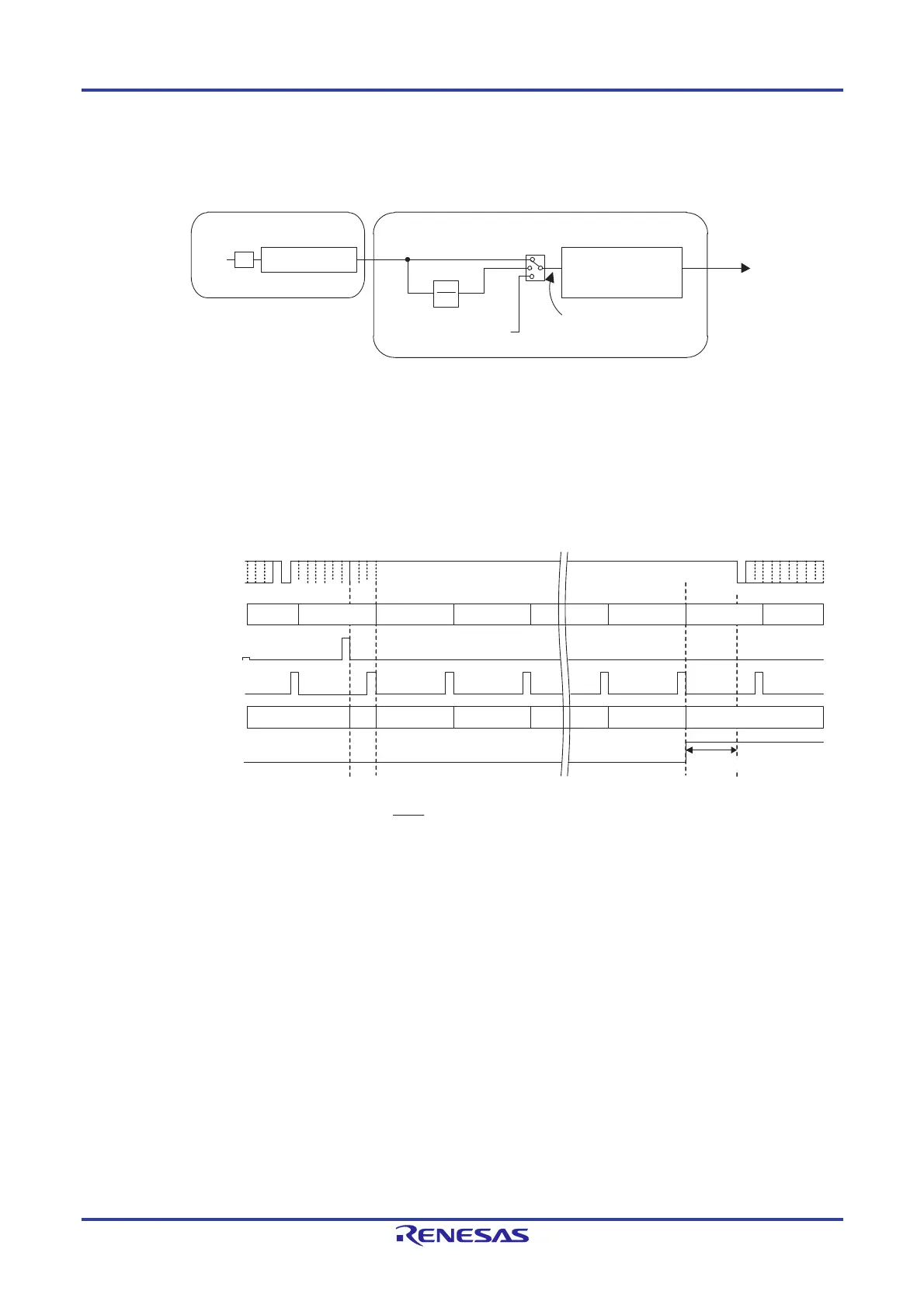

Figure 18-8 shows the interval timer block diagram.

Figure 18-8. Interval Timer Block Diagram

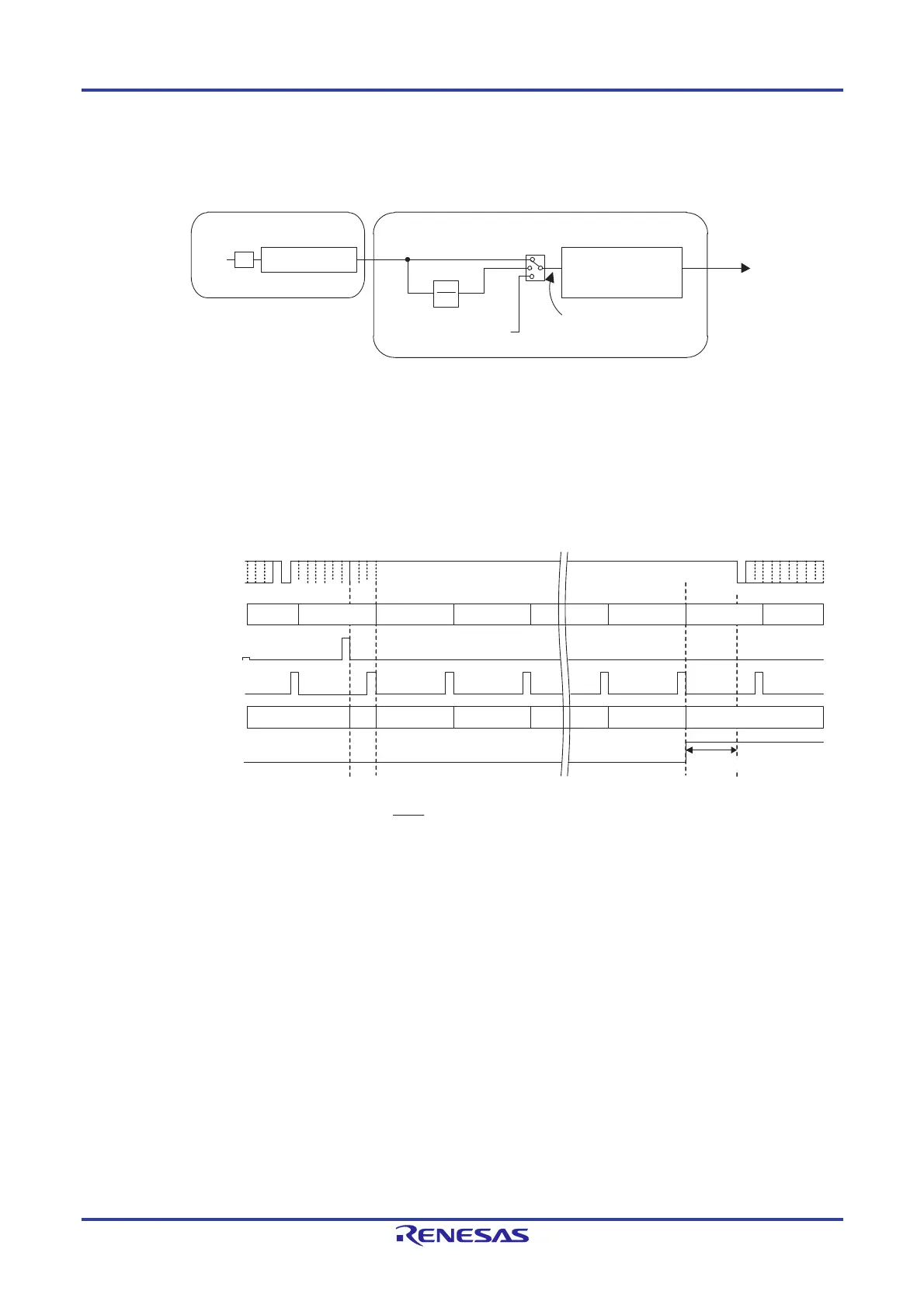

Figure 18-9 shows the interval timer timing chart.

Figure 18-9. Interval Timer Timing Chart

(1) The interval timer starts counting upon completion of transmission. Since the prescaler is not initialized at the time

of transmission completion, the first interval time contains an error of up to one count of the interval timer.

(2) The interval timer is decremented by the next count enable signal.

(3) When the interval timer has decreased to 0, the transmit/receive FIFO buffer issues a transmit request.

(4) The transmit/receive FIFO buffer is determined for the next transmission by the priority determination, it starts

transmitting data. Transmission starts with a delay of three CANi bit time clock cycles or less from the issue of

transmit request.

1

10

fCLK

ITRCP[15:0]

CFITR,CFITSS

CFITT[7:0]

B'00

B'10

B'x1

CANi bit time clock

Interval timer

(Setting range: 0 to 255)

1/2

Prescaler

Count enable signal

Remark ITRCP[15:0]: Bits in the GCFGH register

CFITR, CFITSS, CFITT[7:0]: Bits in the CFCCHk register (k = 0)

(1) (2) (3) (4)

H

L

1

0

1

0

0 10 9 8 1 0

1

0

1

CAN bus

Prescaler of

ITRCP[15:0]

499

. . .

. . . . . . . . .

. . . . . . . . . . . . . . . . . . . . .

0

EOF INT

ACK

499 0

499 0 499 0 499 0 499 0 499 0 499 0

SOF

fCLK

Remark fCLK : CPU/peripheral hardware clock

ITRCP[15:0]: Bits in the GCFGH register (The set value is 500 in this figure.)

CFITT[7:0]: Bits in the CFCCHk register (The set value is 10 in this figure.)

× 2 × m (ITRCP[15:0] value) × CFITT[7:0] value

Transmit complete signal

Count enable signal

FIFO transmit request

Interval timer

Transmit priority

determination and internal

processing

Interval time (logical value) =

Loading...

Loading...