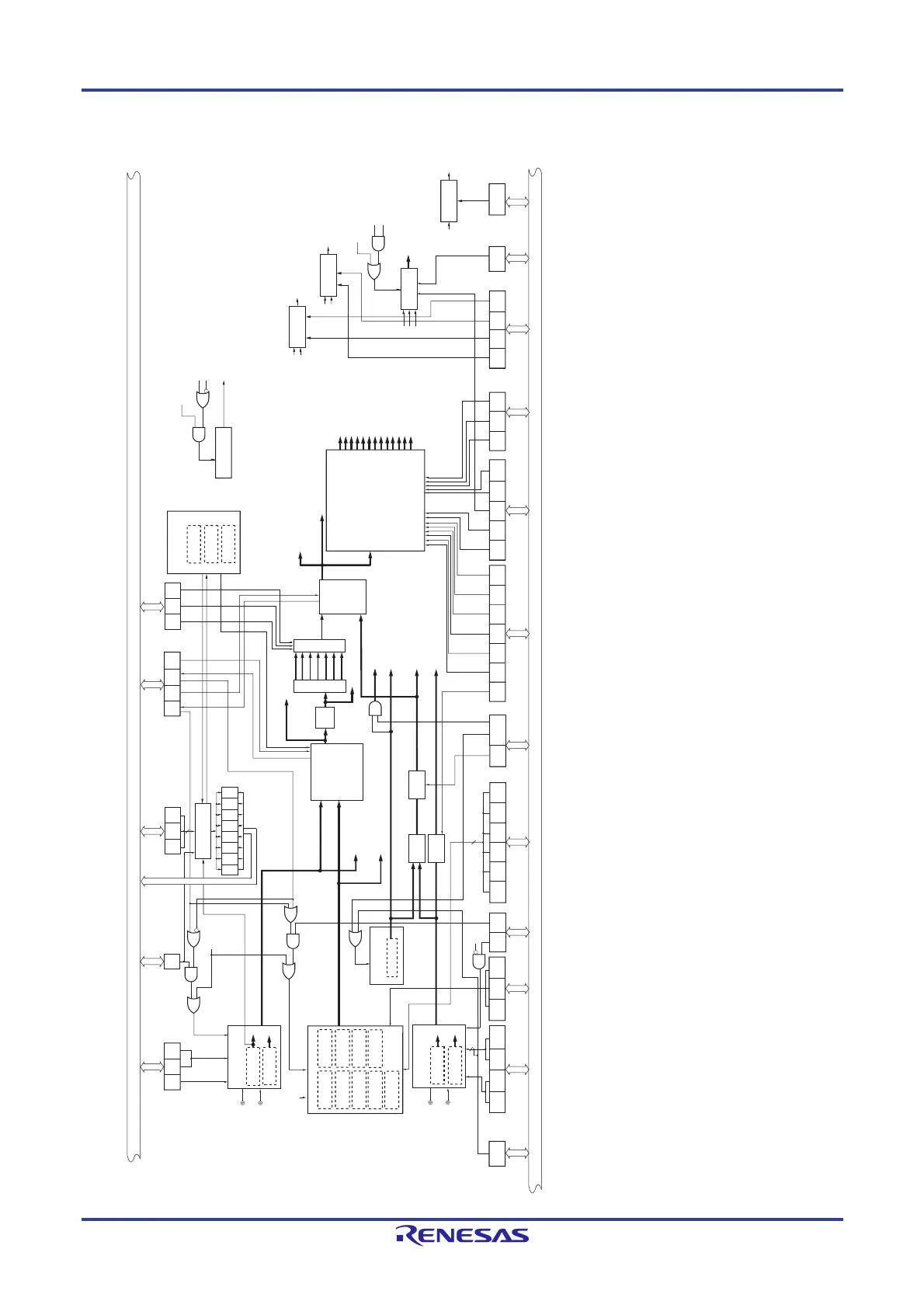

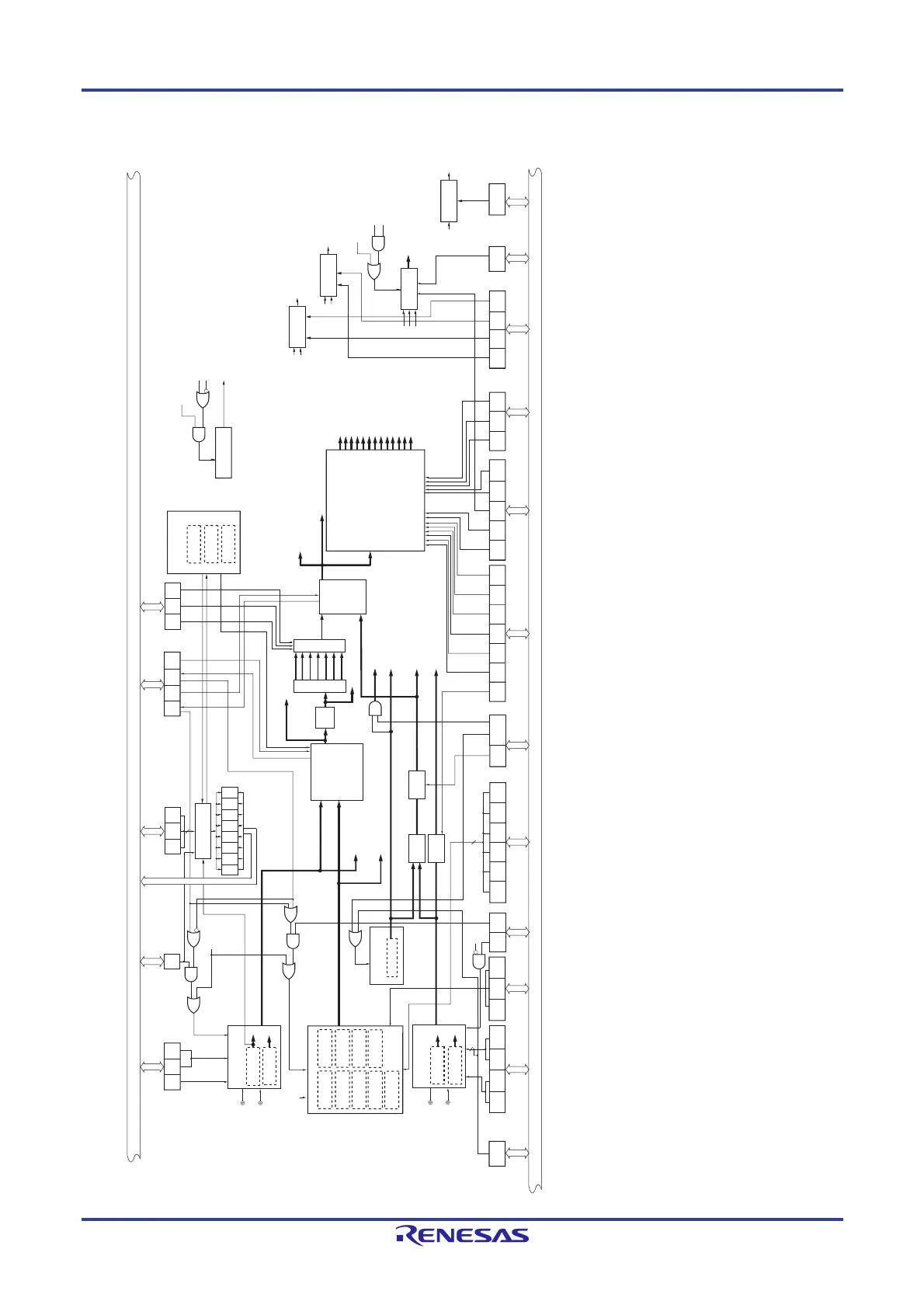

RL78/F13, F14 CHAPTER 5 CLOCK GENERATOR

R01UH0368EJ0210 Rev.2.10 366

Dec 10, 2015

Figure 5-1. Block Diagram of Clock Generator

(Remark is listed on the next page.)

XT1/P123

3

XT2/EXCLKS

/P124

f

SUB

f

CLK

CSSCLS

OSTS1 OSTS0OSTS2 MDIV1 MDIV0MDIV2

3

MOST

18

MOST

17

MOST

15

MOST

13

MOST

11

MS

T

OP

EXCLK

OSCSEL

AMPH

f

MX

f

XT

X1/P121

X2/EXCLK

/P122

f

X

f

EX

MCM0

MCS

CPU

MOST

10

MOST

9

MOST

8

XTSTOP

HIOSTOP

OSCSELSAMPHS0AMPHS1

CLS

f

IH

f

MAIN

f

IL

f

EXS

EXCLKS

HIOTRM0

6

HIOTRM1HIOTRM2

HIOTRM3

HIOTRM4

HIOTRM5

DTC

EN

TRD0

EN

DAC

EN

CMPEN

TRJ0

EN

LIN1

MCK

LIN0

MCKE

LIN1

MCKE

LIN0

MCK

CAN0

EN

LIN0EN

LIN1EN

SAU0

EN

SAU1

EN

IICA0

EN

ADC

EN

TAU1

EN

R

TC

EN

TAU0

EN

HOCODIV2

HOCODIV1 HOCODIV0

RTCLPC WUTMMCK0

SELLOSC

TRD_CKSEL CAN0MCKE

f

MP

f

MP

/32

f

MP

/16

f

MP

/8

f

MP

/4

f

MP

/2

f

MP

f

MP

/64

Internal bus

Internal bus

f

SL

f

WD T

f

M P

f

S L

f

CLK

PLL

(see figure

5-2)

f

CLK

f

MX

f

MX

f

CLK

f

MX

X1 oscillation

stabilization time counter

STOP mode

signal

User option byte (000C2H/020C2H)

FRQSEL0 to FRQSEL4

Standby controller

STOP mode

(64 MHz (TYP.))

PLLDIV1

SELPLLS

Timer RD

Real-time clock

Real-time clock

CAN module

LIN module 0

LIN module 1

On-chip oscillator

for

WDT only

User option byte (000C0H/020C0H)

LIN module 1

LIN module 0

WDSTBYON

User option byte (000C2H/020C2H)

CAN module

FRQSEL4

Clock operation mode

control register

(CMC)

Clock operation status

control register

(CSC)

High-speed system

clock oscillator

External input

clock

Crystal/ceramic

oscillation

High-speed on-chip oscillator

(32 MHz (TYP.))

(16 MHz (TYP.))

(8 MHz (TYP.))

(1 MHz (TYP.))

(48 MHz (TYP.))

(24 MHz (TYP.))

(12 MHz (TYP.))

(4 MHz (TYP.))

Subsystem clock

oscillator

External input

clock

Crystal

oscillation

Clock select

register

(CKSEL)

Clock operation mode

control register

(CMC)

High-speed on-chip

oscillator trimming

register (HIOTRM)

High-speed on-chip

oscillator frequency select

register (HOCODIV)

Clock operation status

control register

(CSC)

Operation speed mode

control register

(OSMC)

Peripheral enable

register 0

(PER0)

Peripheral enable

register 1

(PER1)

Peripheral enable

register 2

(PER2)

Clock select

register

(CKSEL)

CAN clock select

register

(CANCKSEL)

LIN clock select

register

(LINCKSEL)

Low-speed on-chip

oscillator

(15 kHz (TYP.))

Oscillation stabilization

time select register

(OSTS)

Oscillation stabilization

time counter status

register (OSTC)

Main system

clock source

selector

Clock output/

buzzer output

Prescaler

Selector

CPU clock

and

peripheral

hardware

clock source

selection

Clock monitor,

channel 1 of timer array unit

Clock output/buzzer output,

Timer RJ, timer RD

Real-time clock

Controller

Controller

Controller

Controller

Controller

Controller

Timer RJ

Timer RD

Controller

Selector

System clock

control register

(CMC)

f

MP

clock

division register

(MDIV)

HALT mode

Normal operation

mode

Watchdog timer

HALT/STOP mode signal

User option byte (000C0H/020C0H)

WDTON

Timer array unit 0

Timer array unit 1

Serial array unit 0

Serial array unit 1

Serial interface IICA0

A/D converter

Timer RJ

DTC

Comparator

D/A converter

LIN module 0

LIN module 1

CAN module

TimerRD

LIN module 0, LIN module 1

Loading...

Loading...