RL78/F13, F14 CHAPTER 15 SERIAL ARRAY UNIT

R01UH0368EJ0210 Rev.2.10 900

Dec 10, 2015

Figure 15-74. Example of Contents of Registers for Master Transmission of SPI Function

(CSI00, CSI01, CSI10, CSI11) (2/2)

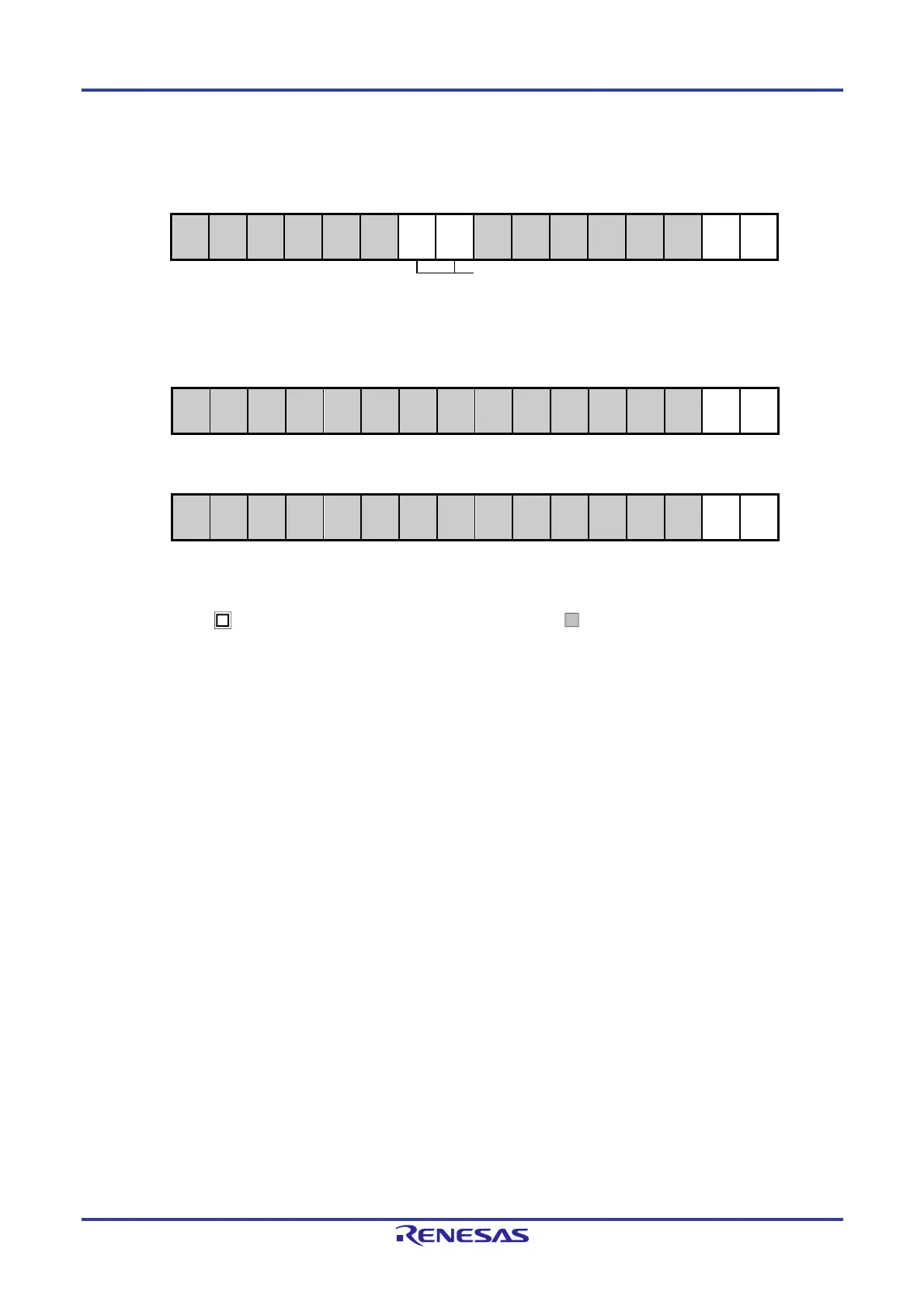

(d) Serial output register m (SOm) … Sets only the bits of the target channel.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SOm

0

0

0

0

0

0

CKOm1

0/1

CKOm0

0/1

0

0

0

0

0

0

SOm1

0/1

SOm0

0/1

Communication starts when these bits are 1 if the clock

phase is forward (the CKPmn bit of the SCRmn = 0). If the

clock phase is reversed (CKPmn = 1), communication

starts when these bits are 0.

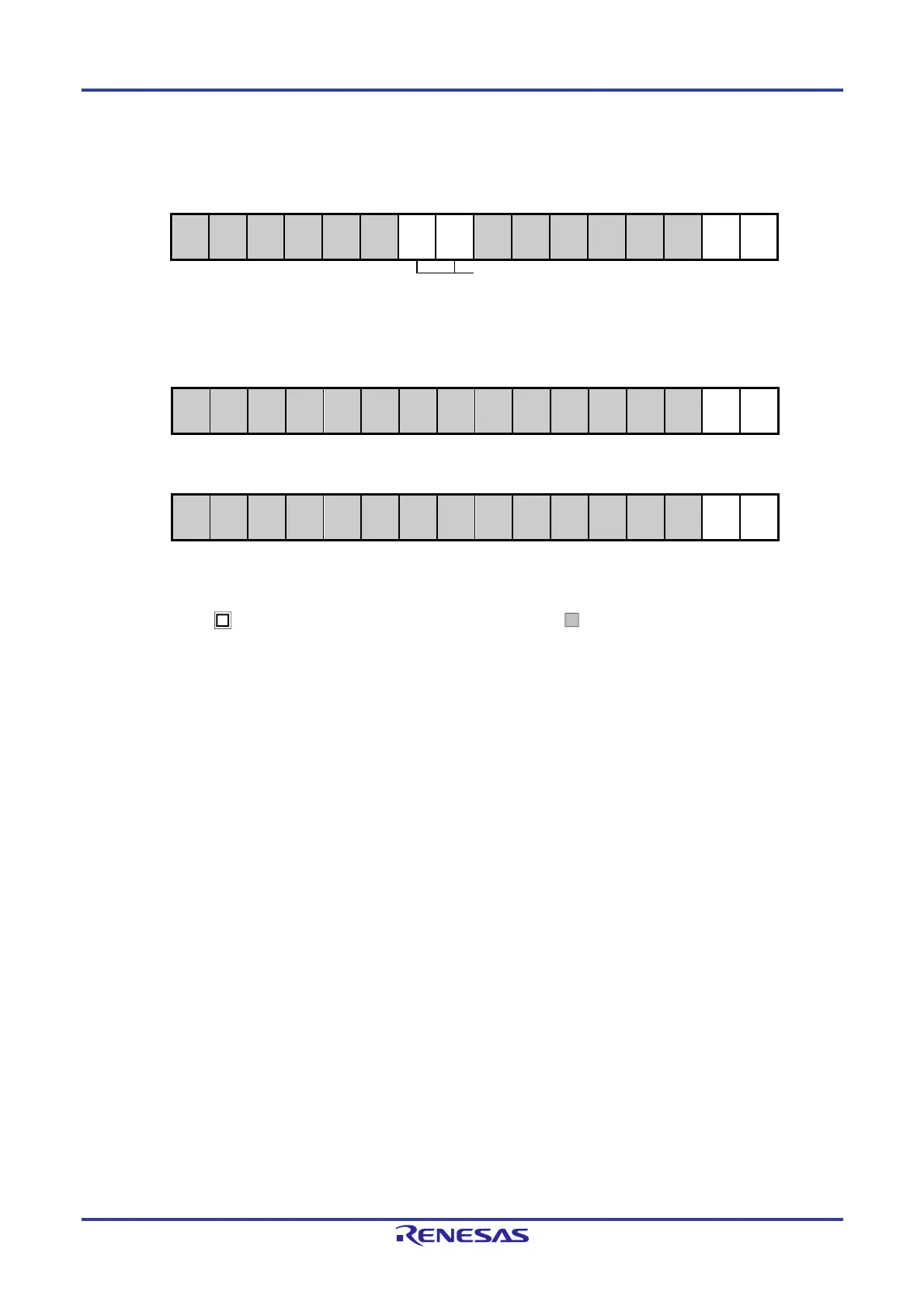

(e) Serial output enable register m (SOEm) … Sets only the bits of the target channel to 1.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SOEm

0

0

0

0

0

0

0

0

0

0

0

0

0

0

SOEm1

0/1

SOEm0

0/1

(f) Serial channel start register m (SSm) … Sets only the bits of the target channel to 1.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SSm

0

0

0

0

0

0

0

0

0

0

0

0

0

0

SSm1

0/1

SSm0

0/1

Remarks 1. m: Unit number (m = 0, 1), n: Channel number (n = 0, 1), p: CSI number (p = 00, 01, 10, 11),

mn = 00, 01, 10, 11

2. : Setting is fixed in the CSI master transmission mode, : Setting disabled (set to the initial value)

0/1: Set to 0 or 1 depending on the usage of the user

Loading...

Loading...