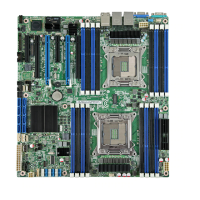

Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Functional Architecture

Revision 1.8

Intel order number E39529-013

21

3.1.3 Enterprise South Bridge Interface (ESI)

One x4 ESI link interface supporting PCI Express Gen1 (2.5 Gbps) transfer rate for connecting

Intel

®

ICH10R in the Intel

®

Server Boards S5520HC, S5500HCV and S5520HCT.

3.1.4 Manageability Engine (ME)

An embedded ARC controller is within the IOH providing the Intel

®

Server Platform Services

(SPS). The controller is also commonly referred to as the Manageability Engine (ME).

3.1.5 Controller Link (CL)

The Controller Link is a private, low-pin count (LPC), low power, communication interface

between the IOH and the ICH10 portions of the Manageability Engine subsystem.

Loading...

Loading...