RL78/F13, F14 CHAPTER 8 TIMER RD

R01UH0368EJ0210 Rev.2.10 629

Dec 10, 2015

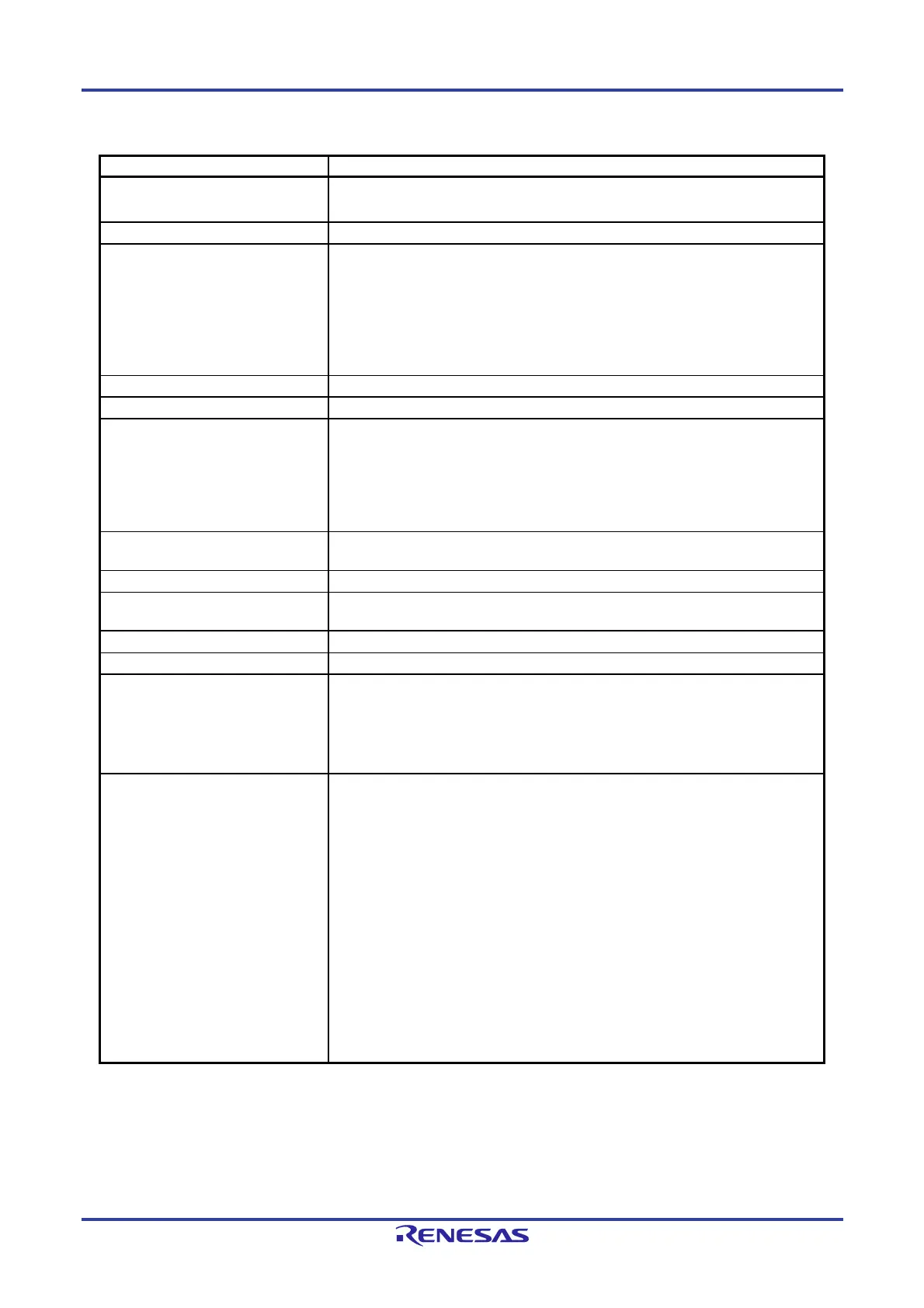

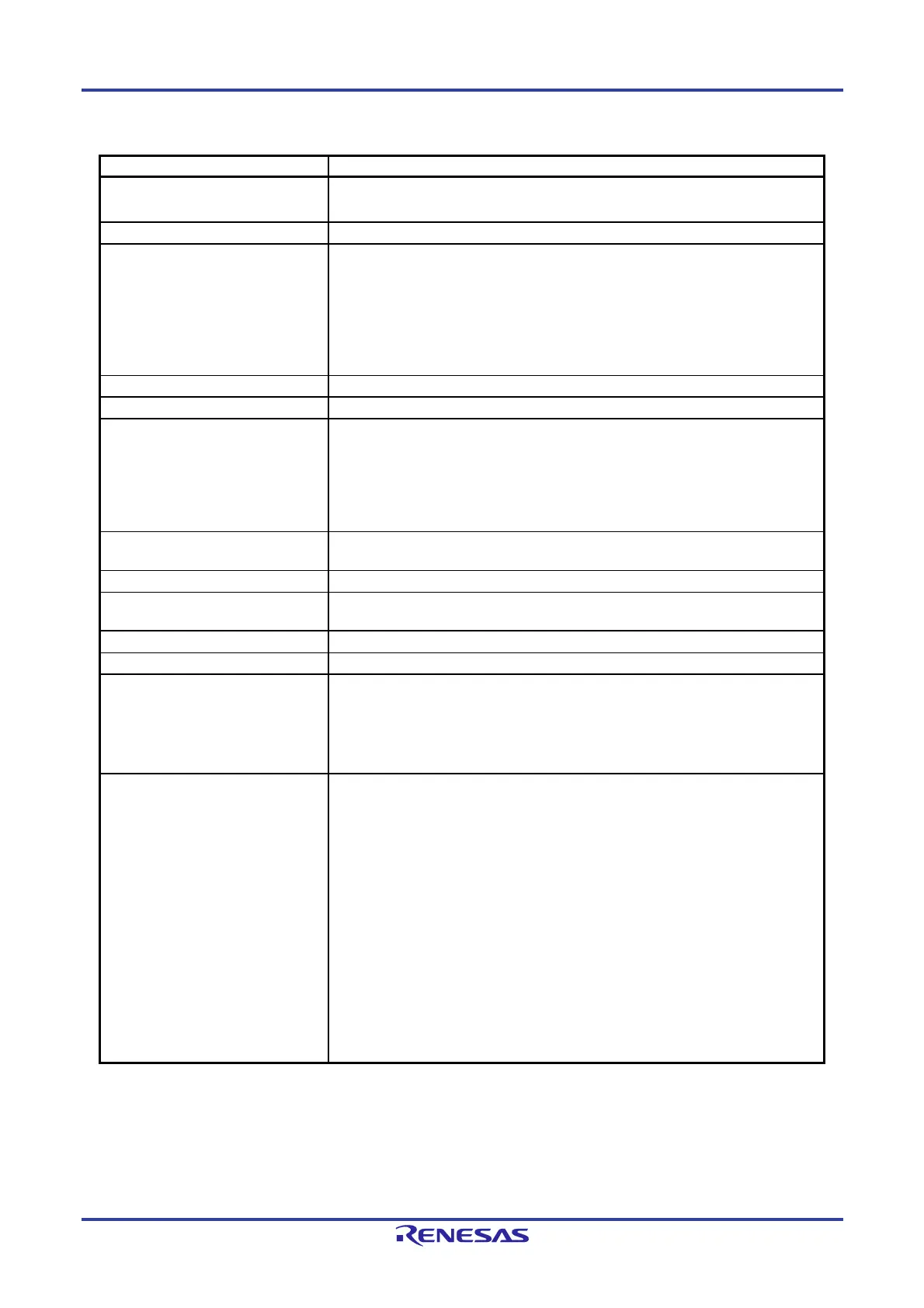

Table 8-15. Output Compare Function Specifications

Item Specification

Count sources

Note

fCLK, fPLL, fIH, fSUB, fIL

External signal input to the TRDCLK0 pin (active edge selected by a program)

Count operations Increment

Count period • When bits CCLR2 to CCLR0 in the TRDCRi register are set to 000B (free-running

operation).

1/fk × 65536 fk: Frequency of count source

• When bits CCLR1 and CCLR0 in the TRDCRi register are set to 01B or 10B

(TRDi register is set to 0000H at compare match with TRDGRji register).

1/fk × (n + 1)

n: Value set in the TRDGRji register

Waveform output timing Compare match (contents of registers TRDi and TRDGRji match)

Count start condition 1 (count starts) is written to the TSTARTi bit in the TRDSTR register.

Count stop conditions • 0 (count stops) is written to the TSTARTi bit in the TRDSTR register when the CSELi

bit in the TRDSTR register is set to 1.

The output compare output pin holds the output level before the count stops.

• When the CSELi bit in the TRDSTR register is set to 0, the count stops at the

compare match with the TRDGRAi register.

The output compare output pin holds the level after output change by compare match.

Interrupt request generation timing • Compare match (contents of registers TRDi and TRDGRji match)

• TRDi register overflow

TRDIOA0 pin function I/O port, output-compare output, or TRDCLK (external clock) input

TRDIOB0, TRDIOC0, TRDIOD0,

TRDIOA1 to TRDIOD1 pin function

I/O port or output-compare output (selectable for each pin)

INTP0 pin function Port or INTP0 interrupt input

Read from timer The count value can be read by reading the TRDi register.

Write to timer • When the TRDSYNC bit in the TRDMR register is set to 0 (timer RD0 and timer RD1

operate independently). Data can be written to the TRDi register.

• When the TRDSYNC bit in the TRDMR register is set to 1 (timer RD0 and timer RD1

operate synchronously). Data can be written to both the TRD0 and TRD1 registers by

writing to the TRDi register.

Selectable functions • Output-compare output pin selection

Either one pin or multiple pins of TRDIOAi, TRDIOBi, TRDIOCi, and TRDIODi.

• Output level selection at compare match

Low output, high output, or inverted output level

• Initial output level selection

The level can be set for the period from the count start to the compare match.

• Timing for setting the TRDi register to 0000H

Overflow or compare match in the TRDGRAi register

• Buffer operation (see 8. 3. 1 (2) Buffer Operation)

• Synchronous operation (see 8. 3. 1 (3) Synchronous Operation)

• Changing output pins for registers TRDGRCi and TRDGRDi

The TRDGRCi register can be used as output control of the TRDIOAi pin and the

TRDGRDi register can be used as output control of the TRDIOBi pin.

• Pulse output forced cutoff signal input (see 8. 3. 1 (4) Pulse Output Forced Cutoff)

• Timer RD can be used as the internal timer without output.

Note When selecting the count source for the timer RD, set the same clock source as the count source for fCLK before

setting bit 4 (TRD0EN) in the peripheral enable register 1 (PER1).

Remark i = 0 or 1, j = A, B, C, or D

Loading...

Loading...