Tripping logic

ABB Network Partner AB

1MRK 580 120-XEN

Page 5 - 3

Version 1.0-00

Signal To phase...

L1TRIP L1

L2TRIP L2

L3TRIP L3

External tripping signals can also cause a single-phase tripping without

any restriction.

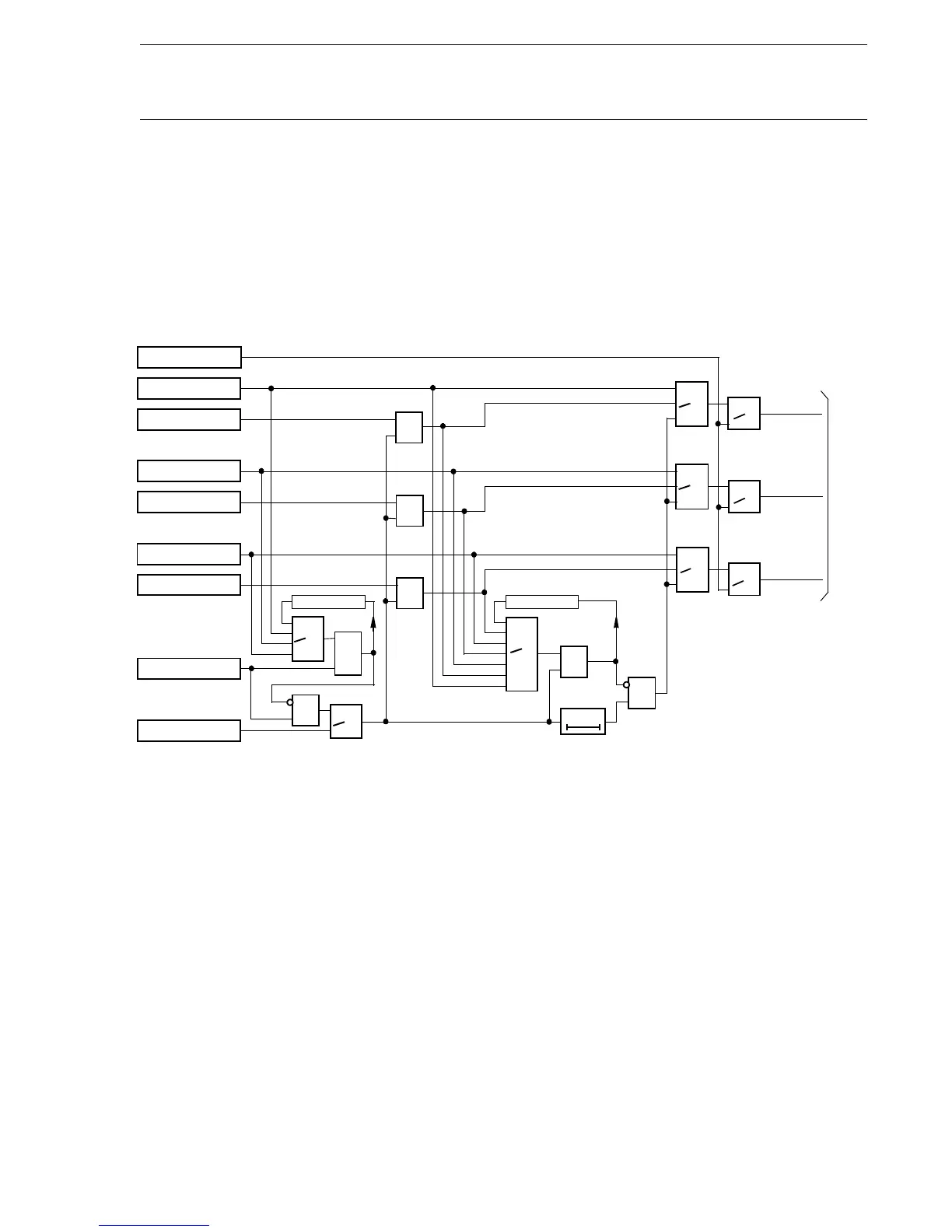

Fig. 2 Single-phase front logic—simplified logic diagram

You can configure the TRIP-TRSPE signal to the output signal of the EF-

--TREF overcurrent, earth-fault, protection function (directional and non-

directional). This enables single-phase tripping when the faulty phase is

detected by some other phase-selection element such as the phase selec-

tion in distance protection.

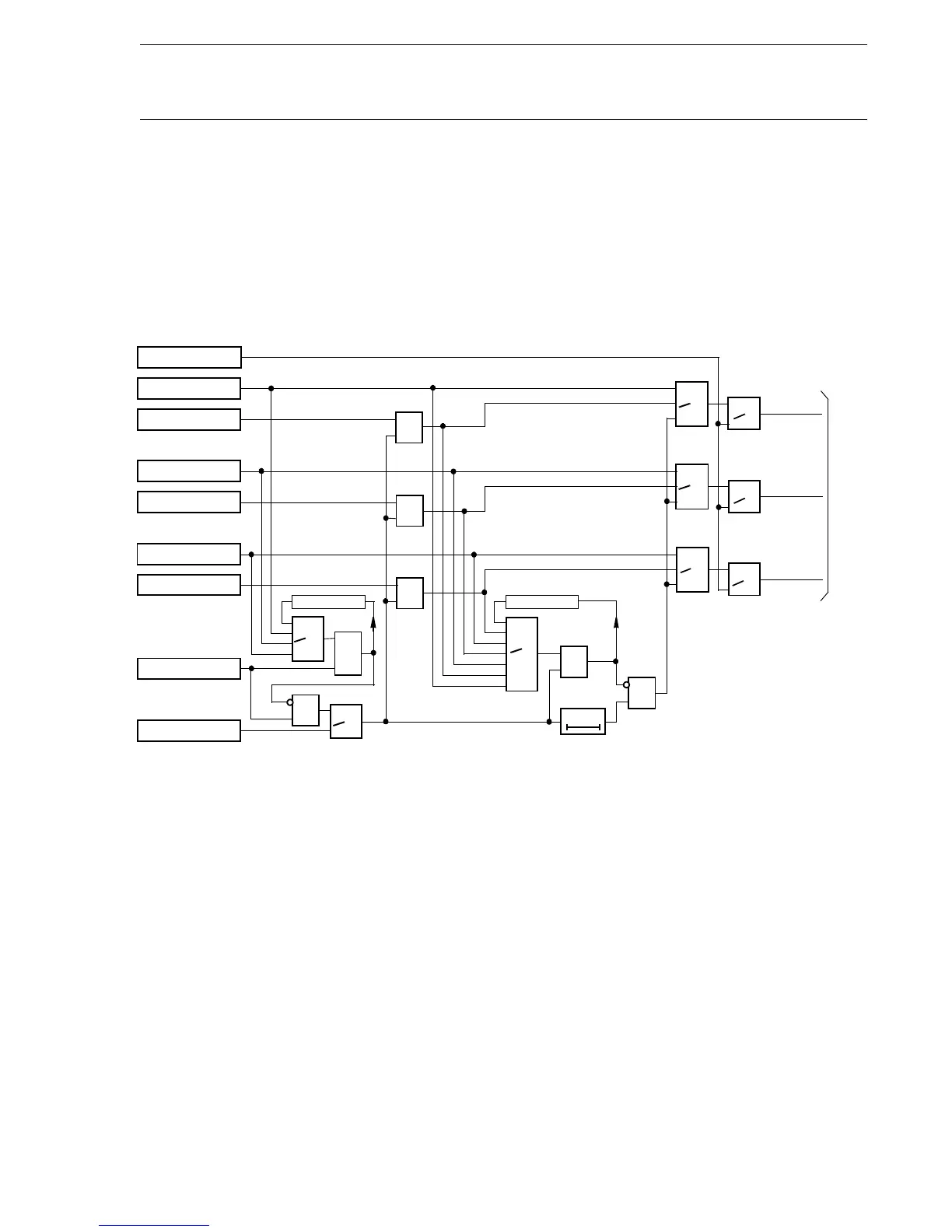

2.3 Tripping logic circuits Fig. 3 shows a simplified illustration of the tripping logic circuits. The

TRIP-BLOCK signal might block the operation of the complete tripping

unit. In a similar way, an external TRIP-EXTTRIP signal can cause

instantaneous three-phase tripping if the function has not been blocked by

external signal or the terminal has been switched to operational testing

mode with activated blocking. A functional TRIP-PTPTRIP input signal

prepares the three-phase tripping conditions for any of the tripping signals

arriving from the front logics. Timers, delayed for 2 seconds at drop-out,

assure correct three-phase tripping for evolving faults.

TRIP-TRTP

TRIP-EXTL1

TRIP-PSL1

TRIP-EXTL2

TRIP-PSL2

1

V

1

V

1

V

L1TRIP

L2TRIP

L3TRIP

To

Fig 3

TRIP-EXTL3

TRIP-PSL3

TRIP-TRSPE

TRIP-TRSPZ

t

50ms

Loop delay

&

&

1

V

&

&

&

&

Loop delay

1

V

&

1

V

1

V

1

V

1

V

(X80120-2)

Loading...

Loading...