RIGOL 7 Protocol Decoding

7-2 DS6000 User’s Guide

Parallel Decoding

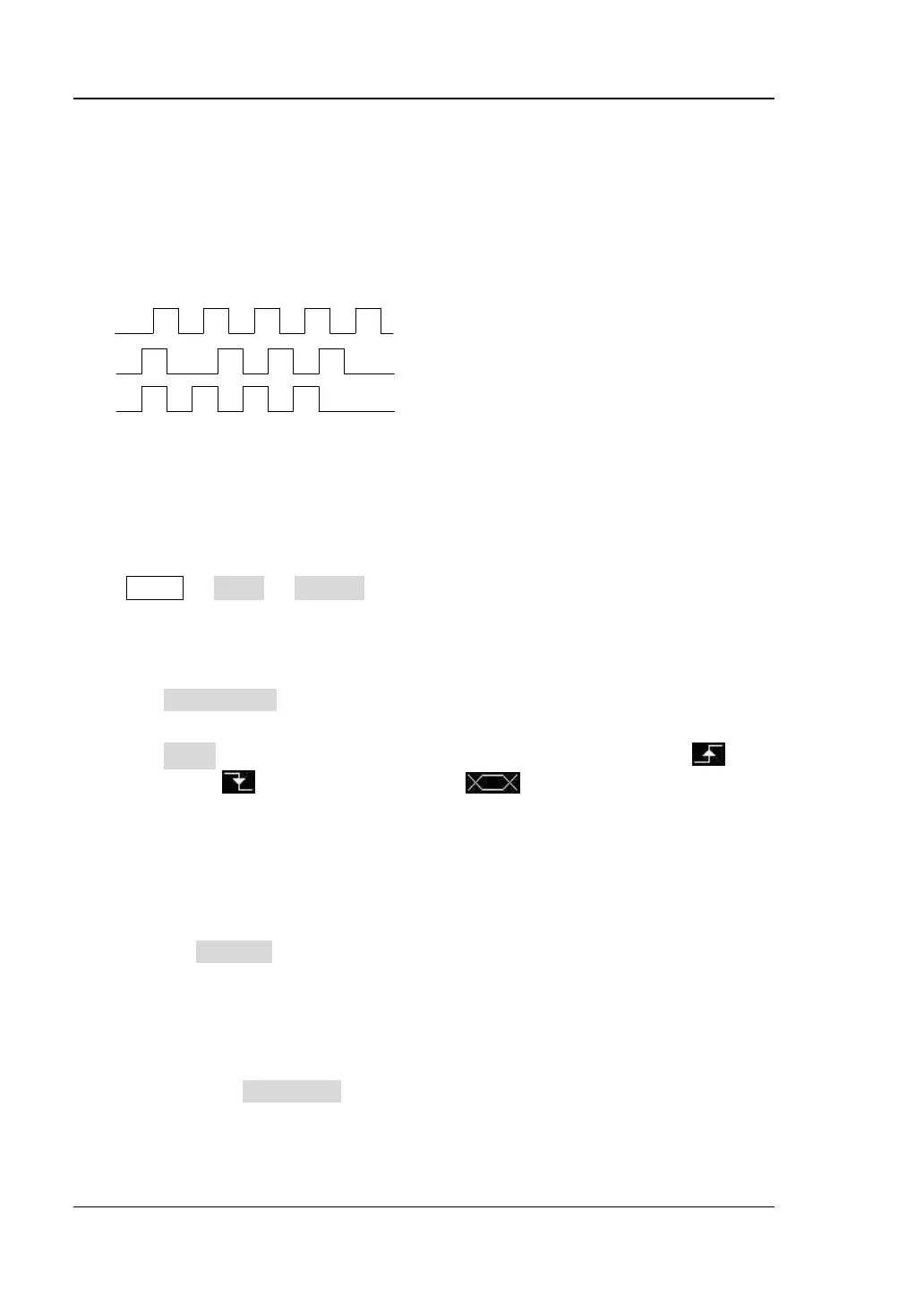

Parallel bus consists of clock line and data line. As shown in the figure below, CLK is

the clock line, while Bit0 and Bit1 are the 0 bit and 1 bit on the data line respectively.

The oscilloscope will sample the channel data on the rising edge, falling edge or the

rising&falling edges of the clock and judge whether each data point is logic "1" or

logic "0" according to the preset threshold level.

Press MATH BUS1 Decode to select "Parallel" and turn on the parallel

decoding function menu.

1. Clock Line Setting (CLK)

Press CLKChannel to select any channel (CH1-CH4) as the clock channel. If

"None" is selected, no clock channel is set.

Press Slope to select to sample the channel data on the rising edge ( ),

falling edge (

) or rising&falling edges ( ). If clock channel is not

selected, the instrument will sample when the channel data jumps in the

decoding.

2. Data Line Setting

Set the bus bits

Press Bus Bits to set the data width of the parallel bus namely the number

of bits per frame. The default is 1 and the maximum is 4 bits (Bit0, Bit1, Bit2,

Bit3).

Specify data channel for each bit.

First, press CurrentBit to select the bit that need to specify channel. The

default is 0 and the range available is always 1 smaller than the data width.

For example, when the data width is 4, the range available is 0, 1, 2, 3.

Loading...

Loading...